主题中讨论的其他器件:CLOCKTREETOOL、 TMDX654GPEVM

您好!

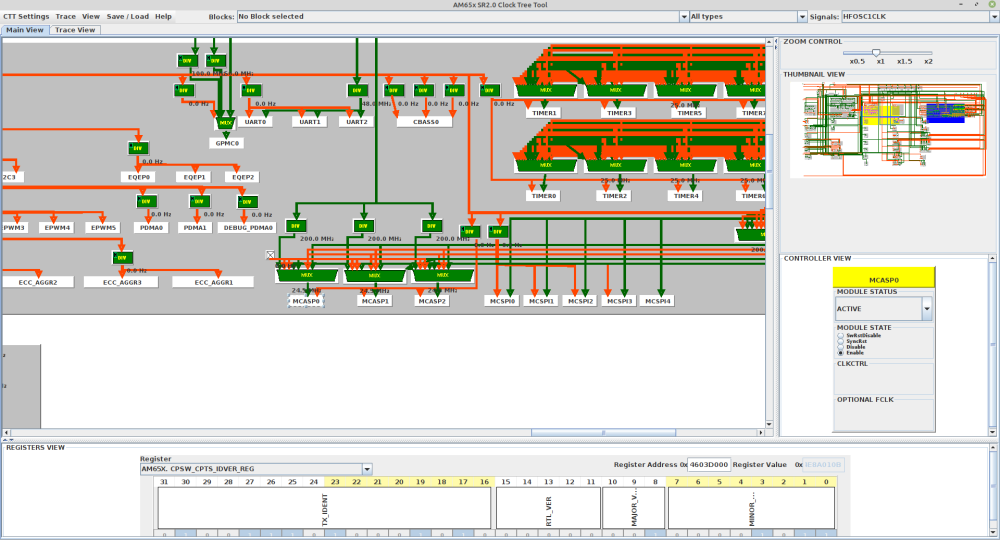

我正在对 McASP0_AHCLKX 不输出任何时钟的问题进行一些研究。 我通过 OBSCLK 引脚跟踪内部时钟、在第5.4.5章模块时钟分配(第2264页、SPRUID7D)中可以找到 MCASP 内核由 PLL2 (PER1_PLL)("PLL2 (PER1 PLL):PRU_ICSSG 内核、MCASP、MMCSD1、GPU、GPMC")计时的内部时钟。

因此、我在 GP EVM 上的 OBSCLK (TIMER_IO1、J19.2)上放置 PER1_PLL、并发现它是一个大约+1.8V 的静态信号、我在这里期望得到25MHz 的 HFOSC0。

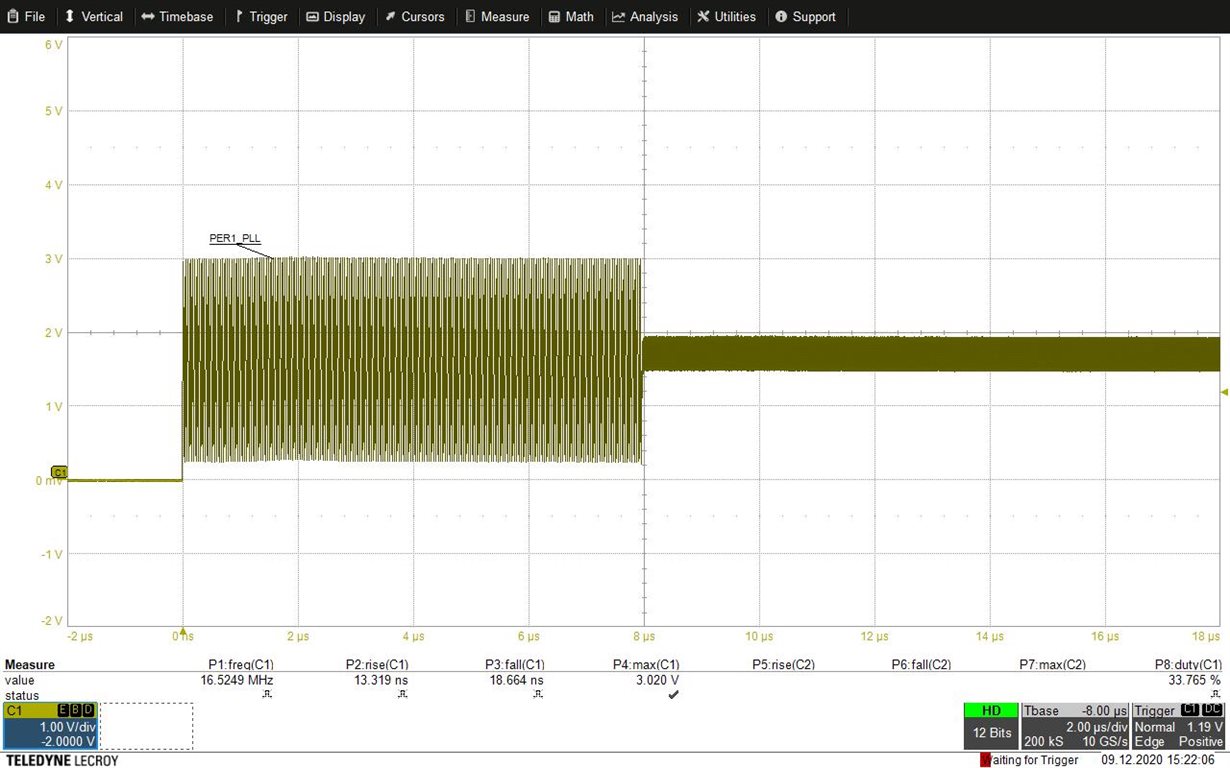

将 PER1_PLL 输入切换为 EXT_REFCLK1、然后切换回 HFOSC0/1、得到您可能在下图中看到的信号。

示波器信号显示 OBSCLK 输出、在本例中设置为观察 PER1_PLL。 它从左侧开始、输入来自 EXT_REFCLK1 (我没有向 EXT_REFCLK1输入信号)。

然后在0us 时、我将 PER1_PLL 输入切换到 HFOSC0/1 (如果为0或1则无关紧要)。 信号显示 HFOSC0/1的时间大约为8us。

然后、在8us 时、信号转换为大约+1.8V 的静态信号。

1) 1)这种行为的原因是什么?

2) 2)如何修复此行为?

3) 3) PER1_PLL 的这种行为是否是 McASP0无法生成 AHCLKX 的原因?

4) 4)为了验证输入时钟、我测量了 WKUP_LFOSC_XI 并发现它在+2.5V 时是静态的、而 PAD 的 I/O 电压为1.8V、RTC (U91)的电源为3.3V。

这似乎很奇怪。 这(静态、电压)是否为误差?

要重新生成上述信号、请在 U-Boot 中输入以下命令:

-将示波器连接到 TIMER_IO1

-解锁 CTRL_MMR 分区2: MW 0x00109008 0x68EF3490;MW 0x0010900C 0xD172BC5A

-解锁 CTRL_WKUP_MMR 分区2: MW 0x43009008 0x68EF3490;MW 0x4300900C 0xD172BC5A

-选择 PER1_PLL 作为 OBSCLK 的信号源: MW 0x00108000 0x5

-用于运行 OBSCLK 的多路复用器 PAD TIMER_IO1: MW 0x0011c304 0x2

- 选择 EXT_REFCLK 作为 PER1_PLL 的时钟源: MW 0x43008088 0x10

-要产生错误:选择 HFOSC0作为 PER1_PLL 的时钟源: MW 0x43008088 0x0

谢谢、

Michael