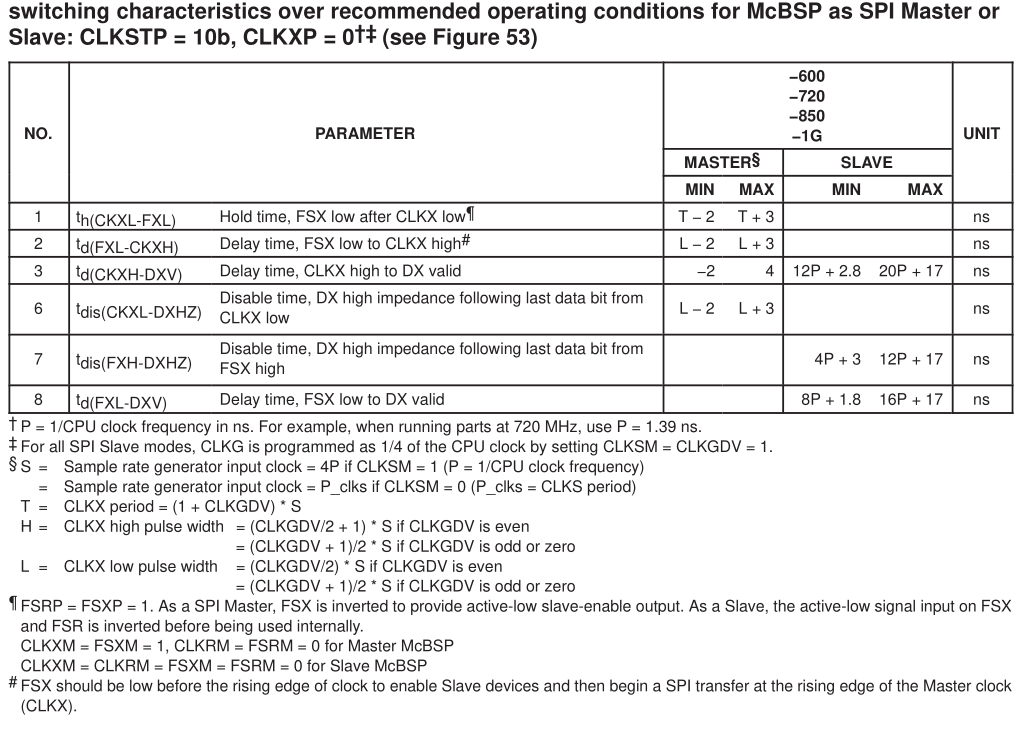

对于作为从器件的 SPI 端口、在任何模式下、数据表将来自时钟的 Dx 有效延迟参数定义为:

12p + 2.8 min 和20P + 17 max、其中 P 是内部 DSP 时钟的周期。

对于 Dx 有效延迟参数定义、常数项(2.8、17)是否仅取决于温度和芯片变化? 如果不是、有哪些依赖关系?

对于 Dx 有效延迟 参数定义,"P"项(12P、20P)是否为变化(12 - 20)仅与 SPI 端口有关的内部 DSP 时序的函数? 是否所有 SPI 配置都存在此变化? 还是在某些配置中更严格? 此"P"项是否可以用于 SPI 配置、DSP 配置和/或温度环境?