您好!

为了更轻松地配置 Sitara GPMC 寄存器、您是否可以提供任何其他信息?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

为了更轻松地配置 Sitara GPMC 寄存器、您是否可以提供任何其他信息?

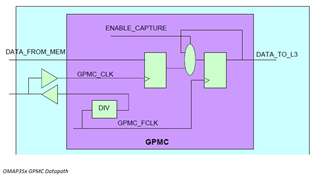

下图给出了 GPMC 数据路径的简化概述。 在同步模式下、首先在 GPMC_CLK 上升沿捕获来自闪存的数据、然后在 GPMC_FCLK 上升沿捕获数据。 第二个捕获由考虑 RDACCESSTIME、WAITMONITORING 和 GPMCFCLKDIVIDER 的逻辑启用。

注意: 当 GPMC 配置为同步模式时、GPMC_CLK 信号( 即输出)也必须设置为输入(CONTRAL.CONTINL_PADCONF_GPMC_NCS7[24] INPUTENABLE1 = 1)。 GPMC_CLK 在 器件边界通过相应 GPMC_CLK 焊盘的输出和输入缓冲器环回。 环回时钟用于 同步存储器信号的采样。

重要的一点是、第二次捕获将在周期编号:·RDACCESSTIME+1、如果 GPMCFCLKDIVIDER 为0 (GPMC_CLK = GPMC_FCLK)、·RDACCESSTIME+2、如果 GPMCFCLKDIVIDER 大于0 (GPMC_CLK = GPMC_FCLK = GPMC_FCLK 除以3或2)时发生。

由于 GPMC_CLK 的最大速度为100MHz、因此第一个采样触发器(在 GPMC_CLK 上)和第二个采样触发器(在 GPMC_FCLK 上)之间的逻辑路径的持续时间为10ns。

第1条. PAGEBURSTACCESSTIME 必须是 GPMCFCLKDIVIDER+1的倍数。

对于同步访问、每次突发的访问时间必须考虑 GPMC 模块的时钟分频器。

例如、如果 L3时钟为166MHz、则必须通过设置 GPMCFCLKDIVIDER=1 (即2分频)来降低 GPMC_CLK。

GPMC_FCLK = 166MHz GPMC_CLK = 83MHz

因此,PAGEBURSTACCESSTIME 必须是2的倍数(这也意味着至少2的倍数)。 因此、如果将 PAGEBURSTACCESSTIME 设置为4、则突发周期将为2个 GPMC_CLK 周期长。

第2条. (RDCYCLETIME–CLKACTIVATIONTIME)必须是 GPMCFCLKDIVIDER+1的倍数。

与规则1类似、这也可确保同步访问在 GPMC_CLK 和 GPMC_FCLK 上都以上升沿结束。

第3条. (RDACCESSTIME–CLKACTIVATIONTIME)模数(GPMCFCLKDIVIDER + 1)必须不同于 GPMCFCLKDIVIDER

这是 OMAP3内部采样方案的结果(请参阅上面的方框图)。 违反此规则不会导致功能中断、而是会限制最大 GPMC_CLK 频率。

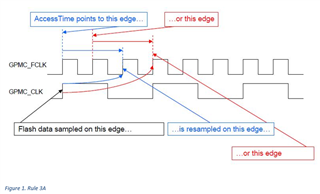

图1说明了遵循规则3时的采样时序。 蓝色轨迹显示的是(RDACCESSTIME - CLKACTIVATIONTIME)%2 = 0时的情况、红色轨迹显示的是(RDACCESSTIME - CLKACTIVATIONTIME)%2 = 1时的情况。

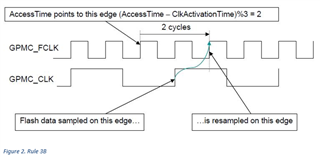

图2显示了违反规则3的示例。 数据在初始采样后仅在一个时钟周期内重新采样。

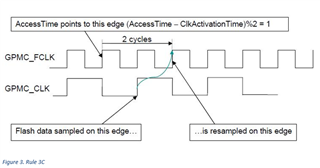

图3显示了违反规则3的示例。 同样、数据在初始采样后仅在一个时钟周期内重新采样。

第4条. 如果 GPMCFCLKDIVIDER 大于0、RDCYCLETIME 必须大于或等于 RDACCESSTIME+2。 如果 GPMCFCLKDIVIDER 为0、RDCYCLETIME 必须大于或等于 RDACCESSTIME+1。

这也是上述采样方案的结果。 如果未遵守规则4、则访问结束(由 RDCYCLETIME 确定)将在第二个触发器上的最后一个数据采样之前发生(在 RDACCESSTIME+1或 RDACCESTIME+2、取决于 GPMCFCLKDIVIDER)。 这将导致 GPMC 状态机未定义的行为。

第5条. 如果 GPMCFCLKDIVIDER 大于0且 WAITREADMONITORING 被启用、则 CSRDOFFTIME 必须大于或等于 RDACCESSTIME+2。 如果 GPMCFCLKDIVIDER 为0且 WAITREADMONITORING 被启用、则 CSRDOFFTIME 必须大于或等于 RDACCESSTIME+1

此规则是上述采样方案的另一个结果。 在 GPMC 的同步模式下、启用等待监控后、内部 GPMC 状态机会查找等待置位/置位。 在这种情况下、状态机被设计成需要一个额外的时钟周期。 如果 CSRDOFFTIME 不考虑这个额外的时钟周期、GPMC 状态机将进入一个未定义状态。

第6条. 如果 GPMCFCLKDIVIDER 大于0且 WAITREADMONITORING 被启用、OEOFFTIME 必须大于或等于 RDACCESSTIM+2。 如果 GPMCFCLKDIVIDER 为0且 WAITREADMONITORING 被启用、OEOFFTIME 必须大于或等于 RDACCESSTIME+1。

其原因与规则5相同、但它适用于 OE 信号。

第7条. 无论 WAITREADMONITORING 和 GPMCFCLKDIVIDER 如何、OEOFFTIME 和 CSRDOFFTIME 必须大于或等于 RDACCESSTIME+1。

此规则是 GPMC 状态机实现的结果:对于同步突发访问、GPMC 状态机在 AccessTime 后花费一个周期来冻结控制 CsRdOffTime 和 OeOffTime 的计数器。

以软件执行双字突发为例、RDACCESSTIME = OEOFFTIME。 在 RDACCESSTIME+1时、GPMC 状态机将 PAGEBURSTACCESSTIME 添加到 OEOFFTIME 中、但在该周期结束时将 OE 置为无效已经太晚了。 这会导致 OE 在周期之后失效。 CS 和更长的突发访问也是如此。