工具与软件:

您好!

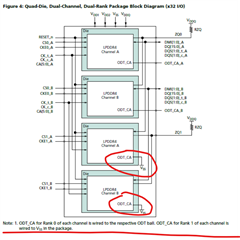

我们使用 Micron: MT53E2G32D4DE-046 AAT:C、您可以看到 Rank1 ODT_CA 连接到 VSS、这意味着没有地址线终端?

看起来在我们的原型板上正常工作:

我注意到:

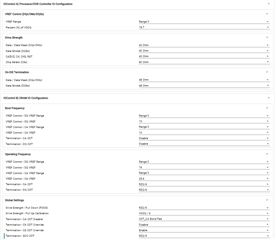

终端- SOC ODT:RZQ/5

终端- CA ODT:RZQ/3

终端- DQ ODT:RZQ/6

问题1: 为什么我们必须将 CA ODT 设置为与 SOC ODT 不同?

我认为、我们应该将 CA ODT 和 DQ ODT 设置为与 SOC ODT = RZQ/5 => 48欧姆相同。

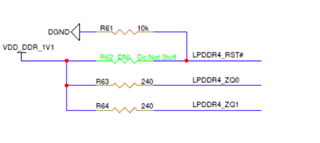

查看我们的原理图:

问题2:您能为每个存储器通道(A、B)提供 MR11和 MR22寄存器的值吗?

Q3:SoC LPDDR4驱动器能够支持40 Ω/60 Ω、下拉电阻为120 Ω?

Q4: Rank0、CLK/CS/CA ODT 终端是否已启用?

Q5:是否禁用 Rank1、CLK/CS/CA ODT 终端?

谢谢

最大值