工具与软件:

您好!

我写信询问 AM623的 GPMC 时序。

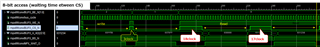

我们在 GPMC 中遇到读取访问问题、即两次读取访问之间的延迟极长、大约17-18个时钟周期。

相比之下、两次写访问之间的延迟仅为3个时钟周期、使得读访问间隔明显更长。

GPMC 连接到 FPGA。

GPMC 设置

・GPMC 和 NOR 闪存。 同步单次读取(GPMCFCLKDIVIDER = 0)

・DMA 未使用

・CYCLE2CYCLEDELAY:1.

・CYCLE2CYCLESAMECSEN:1.

・CYCLE2CYCLEDIFFCSEN:1.

・BUSTURNAROUND:1.

请提供以下三个问题的信息:

1.两次读取访问之间的延迟时间是否合理?

2.是否可以减少延迟?

3.使用 DMA 会帮助减少两次读取访问之间的延迟时间吗?

感谢您的帮助。

此致、

Eiji