工具与软件:

尊敬的支持部门:

我正在 am62上的定制电路板上评估 LCD (DPI、RGB888)。

如何将数据输出的时钟极性更改为上升沿驱动?

以下情况得到确认:

1.在 panel-simple.c 中的结构 panel_desc 中将"drm_BUS_FLAG_PIXDATA_DRIVE_POSedge"设置为".bus_FLAGS"

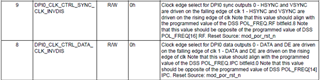

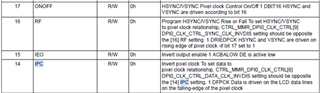

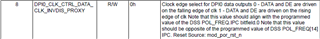

结果:IPC 寄存器被确认为"0"、但 DPI0_CLK_CTRL_DATA_CLK_INVDIS 为"0"。

是否应该将 DPI0_CLK_CTRL_DATA_CLK_INVDIS 设置为1?

从 Linux 中读取寄存器值。

root@am62xx-custom:~# devmem2 0x3020B04C w /dev/mem opened. Memory mapped at address 0xffffafc72000. Read at address 0x3020B04C (0xffffafc7204c): 0x00063000 root@am62xx-custom:~# devmem2 0x00108300 w /dev/mem opened. Memory mapped at address 0xffffa1837000. Read at address 0x00108300 (0xffffa1837300): 0x00000000

波形如下: (CH1:CLK、CH2:DATA)

数据在时钟的下降沿输出。 实际上、数据应该在时钟的上升沿输出。

2.将 "drm_BUS_FLAG_PIXDATA_DRIVE_NEGEDGE"设置为 panel-simple.c 上结构体 panel desc 中的".bus_FLAGS"

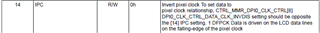

结果:IPC 寄存器被确认为"1"、但 DPI0_CLK_CTRL_DATA_CLK_INVDIS 为"0"。

从 Linux 中读取寄存器值

root@am62xx-custom:~# devmem2 0x3020B04C w /dev/mem opened. Memory mapped at address 0xffff9f4a3000. Read at address 0x3020B04C (0xffff9f4a304c): 0x00067000 root@am62xx-custom:~# devmem2 0x00108300 w /dev/mem opened. Memory mapped at address 0xffff84d14000. Read at address 0x00108300 (0xffff84d14300): 0x00000000

波形如下:

数据在时钟的下降沿输出。 (CH1:CLK、CH2:DATA)

[参考]

SoC:AM6251

电路板:定制电路板

SDK:SDK-AM62X PROCESSOR-SDK-LINUX-RT (版本09.02.01.10)

液晶屏:P0700WVN1MB00 (天马)

设备驱动程序:Panel-simple.c ("CONFIG_DRM_Panel_SIMPLE)

# For LCD timing, add the following to panel-simple.c

@@ -4027,6 +4036,36 @@ static const struct panel_desc yes_optoelectronics_ytc700tlag_05_201c = {

.connector_type = DRM_MODE_CONNECTOR_LVDS,

};

+static const struct drm_display_mode tianma_P0700WVN1MB00_mode = {

+ .clock = 33300,

+ .hdisplay = 800,

+ .hsync_start = 800 + 210,

+ .hsync_end = 800 + 210 + 20,

+ .htotal = 800 + 210 + 20 + 26,

+ .vdisplay = 480,

+ .vsync_start = 480 + 22,

+ .vsync_end = 272 + 22 + 3,

+ .vtotal = 272 + 22 + 3 + 20,

+ .flags = DRM_MODE_FLAG_NVSYNC | DRM_MODE_FLAG_NHSYNC,

+};

+

+static const struct panel_desc tianma_P0700WVN1MB00 = {

+ .modes = &tianma_P0700WVN1MB00_mode,

+ .num_modes = 1,

+ .bpc = 8,

+ .size = {

+ .width = 154,

+ .height = 86,

+ },

+ .delay = {

+ .prepare = 25,

+ .enable = 100,

+ },

+ .bus_format = MEDIA_BUS_FMT_RGB888_1X24,

+ .bus_flags = DRM_BUS_FLAG_DE_LOW,

+ .connector_type = DRM_MODE_CONNECTOR_DPI,

+};

+

@@ -4456,6 +4495,9 @@ static const struct of_device_id platform_of_match[] = {

}, {

.compatible = "yes-optoelectronics,ytc700tlag-05-201c",

.data = &yes_optoelectronics_ytc700tlag_05_201c,

+ }, {

+ .compatible = "tianma,P0700WVN1MB00",

+ .data = &tianma_P0700WVN1MB00,

}, {

/* Must be the last entry */

.compatible = "panel-dpi",

此致、

最终目的