请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TDA4VM 工具与软件:

我使用 TDA4VM、SDK 10.0.08、2.5Gbps PHY 芯片。

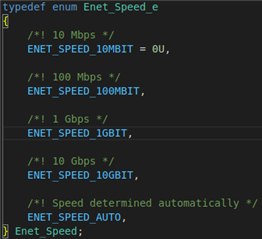

使用 ETHFW。 此处的代码中未定义2.5Gbps、如何将 CPSW9G 的端口1和端口2设置为2.5Gbps 模式?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

Unknown 说:使用 ETHFW。 此处的代码中未定义2.5Gbps、如何将 CPSW9G 的端口1和端口2设置为2.5Gbps 模式?[/QUOT]2.5Gbps 类似于扩展 SGMII、它是 SGMII 时钟的2.5倍。

串行器/解串器需在具有156.25MHz 时钟的 XAUI 接口中配置、而 cpsw 端口必须在 SGMII 中配置、速度为1Gbps。

此致、

Sudheer

要使用 ETHFW CPSW9G、请将端口1和端口2设置为2.5Gbps SGMII。

现在使用以下配置、端口2无法连接外设(此处忽略端口1和外设)。 在哪里配置仍然存在问题?

ethfw/utils/board/src/j721e/board_j721e_evm.c

static EthFwBoard_MacPortCfg gEthFw_gesiMacPortCfg[] =

{

{ /* SGMII-2.5Gbps SerDes-0 LAN0 PHY */

.macPort = ENET_MAC_PORT_1,

.mii = { ENET_MAC_LAYER_GMII, ENET_MAC_SUBLAYER_SERIAL },

.phyCfg =

{

.phyAddr = 0U,

.isStrapped = BFALSE,

.skipExtendedCfg = BFALSE,

.extendedCfg = &gEnetGesiBoard_dp83867PhyCfg,

.extendedCfgSize = sizeof(gEnetGesiBoard_dp83867PhyCfg),

},

.sgmiiMode = ENET_MAC_SGMIIMODE_SGMII_WITH_PHY,

.linkCfg = { ENET_SPEED_1GBIT, ENET_DUPLEX_FULL },

},

{ /* SGMII-2.5Gbps SerDes-0 LAN1 Switch */

.macPort = ENET_MAC_PORT_2,

.mii = { ENET_MAC_LAYER_GMII, ENET_MAC_SUBLAYER_SERIAL },

.phyCfg =

{

.phyAddr = 1U,

.isStrapped = BFALSE,

.skipExtendedCfg = BFALSE,

.extendedCfg = NULL,

.extendedCfgSize = 0,

},

.sgmiiMode = ENET_MAC_SGMIIMODE_SGMII_FORCEDLINK,

.linkCfg = { ENET_SPEED_1GBIT, ENET_DUPLEX_FULL },

},

}

pdk_jacinto_10_00_00_27/packages/ti/board/src/j721e_evm/board_serdes_cfg.c

static Board_STATUS Board_CfgSgmii(void)

{

CSL_SerdesResult result;

CSL_SerdesLaneEnableStatus laneRetVal = CSL_SERDES_LANE_ENABLE_NO_ERR;

CSL_SerdesLaneEnableParams serdesLane0EnableParams = {0};

memset(&serdesLane0EnableParams, 0, sizeof(serdesLane0EnableParams));

/* SGMII Config */

serdesLane0EnableParams.serdesInstance = (CSL_SerdesInstance)SGMII_SERDES_INSTANCE;

serdesLane0EnableParams.baseAddr = CSL_SERDES_16G0_BASE;

serdesLane0EnableParams.refClock = CSL_SERDES_REF_CLOCK_156p25M;

serdesLane0EnableParams.refClkSrc = CSL_SERDES_REF_CLOCK_INT;

serdesLane0EnableParams.linkRate = CSL_SERDES_LINK_RATE_3p125G;

serdesLane0EnableParams.numLanes = 0x2;

serdesLane0EnableParams.laneMask = 0x3;

serdesLane0EnableParams.SSC_mode = CSL_SERDES_NO_SSC;

serdesLane0EnableParams.phyType = CSL_SERDES_PHY_TYPE_XAUI;

serdesLane0EnableParams.operatingMode = CSL_SERDES_FUNCTIONAL_MODE;

serdesLane0EnableParams.phyInstanceNum = SERDES_LANE_SELECT_CPSW;

serdesLane0EnableParams.pcieGenType = CSL_SERDES_PCIE_GEN3;

serdesLane0EnableParams.laneCtrlRate[0] = CSL_SERDES_LANE_FULL_RATE;

serdesLane0EnableParams.loopbackMode[0] = CSL_SERDES_LOOPBACK_DISABLED;

serdesLane0EnableParams.laneCtrlRate[1] = CSL_SERDES_LANE_FULL_RATE;

serdesLane0EnableParams.loopbackMode[1] = CSL_SERDES_LOOPBACK_DISABLED;

CSL_serdesPorReset(serdesLane0EnableParams.baseAddr);

/* Select the IP type, IP instance num, Serdes Lane Number */

CSL_serdesIPSelect(CSL_CTRL_MMR0_CFG0_BASE,

serdesLane0EnableParams.phyType,

serdesLane0EnableParams.phyInstanceNum,

serdesLane0EnableParams.serdesInstance,

0);

CSL_serdesIPSelect(CSL_CTRL_MMR0_CFG0_BASE,

serdesLane0EnableParams.phyType,

serdesLane0EnableParams.phyInstanceNum,

serdesLane0EnableParams.serdesInstance,

1);

result = CSL_serdesRefclkSel(CSL_CTRL_MMR0_CFG0_BASE,

serdesLane0EnableParams.baseAddr,

serdesLane0EnableParams.refClock,

serdesLane0EnableParams.refClkSrc,

serdesLane0EnableParams.serdesInstance,

serdesLane0EnableParams.phyType);

if (CSL_SERDES_NO_ERR != result)

{

return BOARD_FAIL;

}

/* Assert PHY reset and disable all lanes */

CSL_serdesDisablePllAndLanes(serdesLane0EnableParams.baseAddr, serdesLane0EnableParams.numLanes, serdesLane0EnableParams.laneMask);

/* Load the Serdes Config File */

result = CSL_serdesEthernetInit(&serdesLane0EnableParams);

/* Return error if input params are invalid */

if (CSL_SERDES_NO_ERR != result)

{

return BOARD_FAIL;

}

/* Common Lane Enable API for lane enable, pll enable etc */

laneRetVal = CSL_serdesLaneEnable(&serdesLane0EnableParams);

if (CSL_SERDES_LANE_ENABLE_NO_ERR != laneRetVal)

{

return BOARD_FAIL;

}

return BOARD_SOK;

}

如果端口2串行器/解串器配置为以下参数、并且相应的外设也设置为1Gbps、则它可以正常工作。

serdesLane0EnableParams.refClock = CSL_SERDES_REF_CLOCK_100M; serdesLane0EnableParams.linkRate = CSL_SERDES_LINK_RATE_1p25G; serdesLane0EnableParams.phyType = CSL_SERDES_PHY_TYPE_SGMII;

您好!

如果端口2串行器/解串器配置为以下参数、并且相应的外设也设置为1Gbps、则它可以正常工作。

似乎端口2上连接的 PHY 设置为 SGMII 的速率为1Gbps、因此、当您设置相同的 CPSW 串行器/解串器侧时、也能正常工作。

请确保在 XAUI 接口中启用连接到 CPSW 端口2的 PHY/MAC。

此致、

Sudheer