主题中讨论的其他器件:TRF3722、 TRF372017、 DAC3484EVM、 TRF3705

您好!

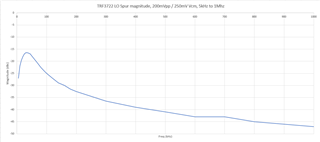

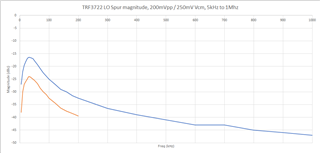

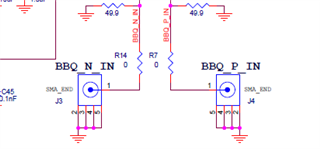

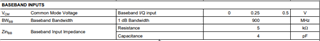

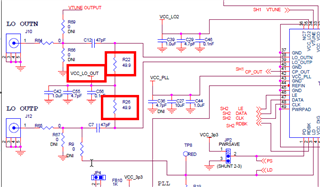

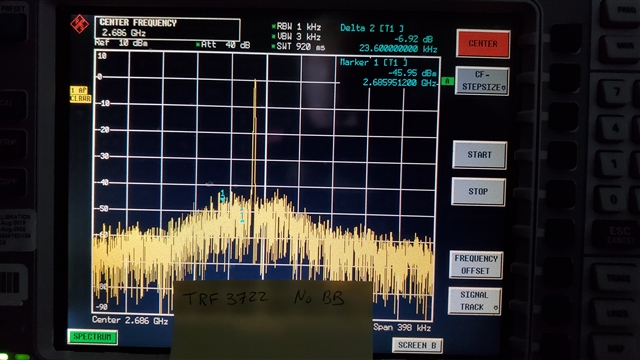

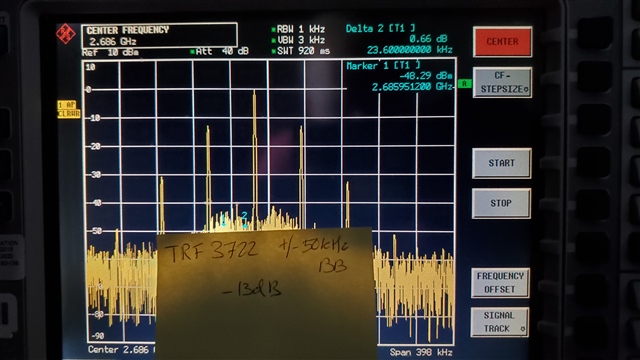

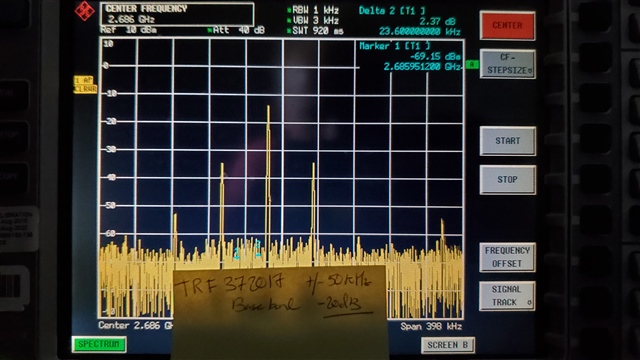

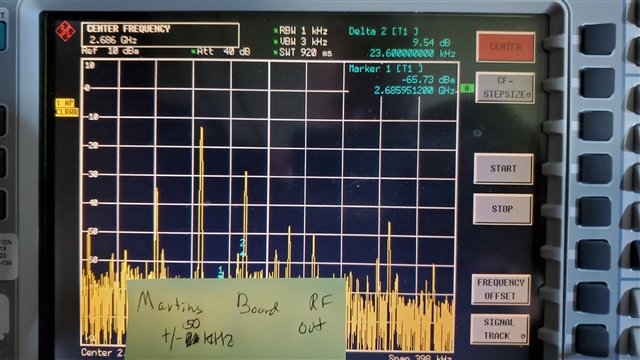

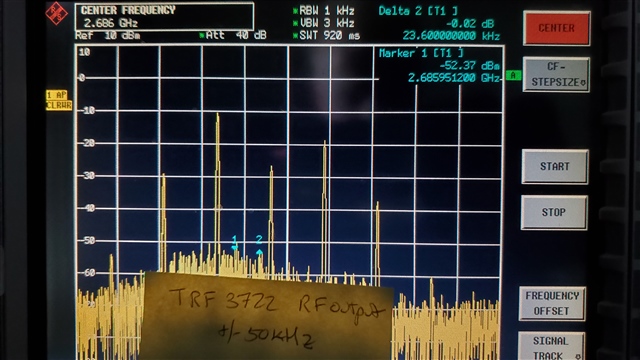

我正在尝试使用 TRF3722设计系统。 我的设计中有一个 PCB、并且还使用 EVM 模块评估了 TRF3722和 TRF372017。 我有一个50kHz I/Q 单频输入、并且使用2.0-3.0GHz PLL 频率(尽管我的许多测试是在2.686GHz 下完成的、但没有特殊原因)。 我在 LO 输出上看到-13dBc 的 IQ 信号。 从理论上讲、LO 输出应该只是 PLL 频率上的单个杂散。 我觉得我一定要做一些傻事、因为我希望对 LO 信号的 I/Q 馈通小于-40至-50dBc。 在本测试中、我一直使用 AFE、其中变压器从单端变为平衡、并能够将偏置点调节到所需的值。 (请原谅我的糟糕的 SpectAn、因为屏幕很暗)。 我已经使用我的设计和评估板对此进行了测试。

我在 TRF372017评估板上看到了同样的行为。

由于看到基带馈通到 LO、我的射频输出是可以达到的峰值。 其中一个预期(在50kHz I/Q 信号下、90度相位)、在 PLL 频率加(或减、具体取决于相位)基带信号50kHz 频率下、产生的输出将是单个杂散。

对我所遗漏的内容有什么想法吗? 谢谢!

在我的板上、所有电源都被旁路掉、以检查和检查、铁氧体隔离、并且与数据表中的应用电路相似。 应用程序使用 IF 频率分析 DSP 中的返回信号以获得准确的相位、并使杂散真正混乱。