此外、如何在 PSpice for TI 的仿真配置文件中添加其他选项?

如果您看到上述消息、以下步骤可能会解决收敛错误: INFO (ORPSIM-16594):要提高伪瞬态收敛和性能、请设置以下选项以放宽电容器电流和电感电压的稳定标准:PTRANABSTOL=1e-5、PTRANVNTOL=1e-4

请注意、修改这些值可能会导致精度降低。 请谨慎使用这些设置。

如果您想在仿真配置文件中添加任何其他选项、请参阅下面的示例以了解该方法。

方法1

- 在 PSpice for TI 中打开原理图设计。 您可以将选项直接添加到设计画布中。 单击"放置" →"文本..." 热键 T。这将打开一个新窗口

- 在新窗口中、键入: @PSpice:.options PTRANABSTOL=1e-5 PTRANVNTOL=1e-4

- 单击 OK (确定)。 单击画布上的任意位置以放置文本框。

- 保存您的设计并运行 PSpice。

- 如果仍然看到收敛错误、可以尝试通过将值更改为 :PTRANABSTOL=1e-4 PTRANVNTOL=1e-3来进一步放宽这些容差。 您还可以打开 Simulation Profile 并选中 AutoConvergence 选项。 请注意、这些不能保证修复、可能会导致精度降低。

方法2

- 在记事本或类似的文本编辑器中、添加此行文本 :+.options PTRANABSTOL=1e-4 PTRANVNTOL=1e-3

- 将名为 include.txt 的文件保存到您选择的位置

- 在 PSpice for TI 中打开您的设计

- 编辑或创建您的仿真配置文件

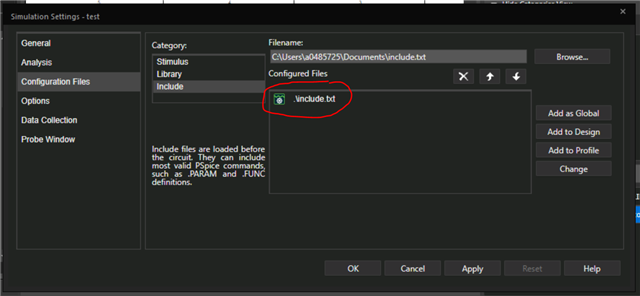

- 在仿真配置文件中、选择"Configuration Files"、然后选择"Include"

- 单击“浏览...” 并导航到您创建的 include.txt 文件

- 单击"添加到配置文件"、并确保它显示在您的已配置文件列表中

- 单击确定、然后再次尝试运行仿真。

- 如果仍然看到收敛错误、可以尝试通过将值更改为 :PTRANABSTOL=1e-4 PTRANVNTOL=1e-3来进一步放宽这些容差。 您还可以打开 Simulation Profile 并选中 AutoConvergence 选项。 请注意、这些不能保证修复、可能会导致精度降低。

这到底意味着什么?

收敛失败意味着仿真器无法找到令人满意的电路解决方案。 这可能是由以下原因造成的:连接不良(即 VDD 轨上无电源、意外接地短路)、模型故障(即设计中出现拼写错误或设计不可能)、容差过小。 在具有振荡的设计中也可能发生这种情况。

容差是可以容忍的误差量。 如果解决方案中的误差低于特定阈值、则将接受该解决方案。 如果高于该阈值、仿真器将再次尝试寻找更好的解决方案。 松开公差(使其更大)将使仿真器更容易找到解决方案。 它还可能更快地找到解决方案。 这些优势可能会以牺牲精度为代价、因为可以容忍更大的误差。

伪瞬态分析是一种用于查找电路直流工作点的算法。 它通常用于许多仿真引擎。 它可能很慢、通常用于其他更快算法无法解决的电路。 PTRANABSTOL 和 PTRANVNTOL 选项用于设置伪瞬态分析的容差。

PTRANABSTOL 的默认值为1e-7安培、PTRANVNTOL 的默认值为1e-5伏。 INFO (ORPSIM-16594)消息表示这些容差可能过小、建议将其放宽至 PTRANABSTOL=1e-5和 PTRANVNTOL=1e-4。 在这种情况下、您应采纳仿真器的建议并按照本常见问题解答中的说明松开公差。 确保对不合理的精度降低保持警惕。

如果您仍然遇到问题、 请单击此处在 PSpice for TI E2E 论坛上打开新主题。