主题中讨论的其他器件:MSP430FW423、 MSP430FW425、

您好!

我们将使用 MSP430FW423/MSP430FW425和 cc115l 作为无线电发送器来生产工作设备。

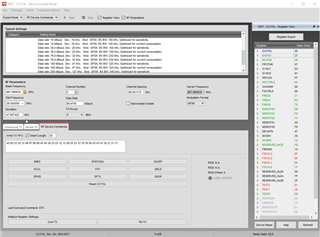

2.我们使用 RFStudio 配置表单、其默认值为"100kb、针对电流消耗进行了优化"。 配置过程显示在 attachment1中,saleae logic2的源代码如下: https://www.dropbox.com/s/whc609zdau98lty/34.C.05%20cc%20configuration%20attachement1.sal?dl=0

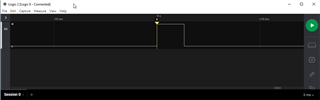

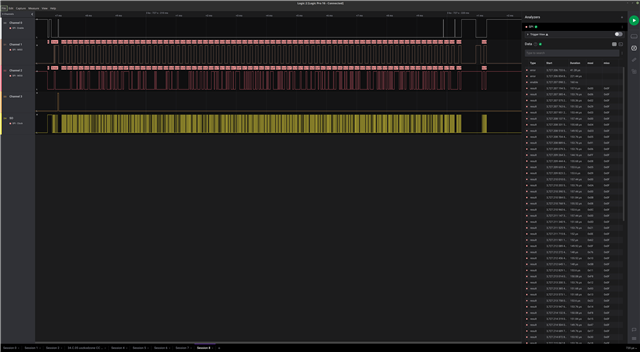

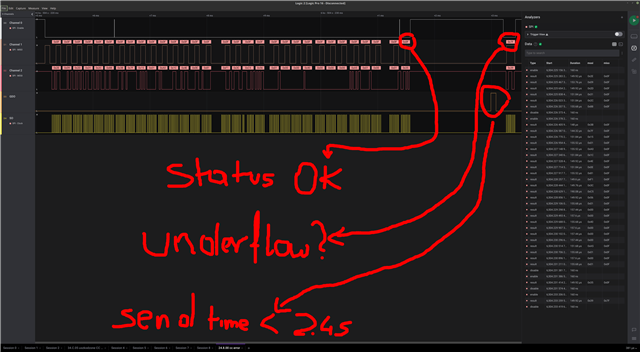

3.我们正在发送数据并对设置为0x06的 GDO 引脚作出反应(发送同步字时生效、在数据包末尾失效)。 如果 TX FIFO 下溢、引脚将取消置位。) 这在高速缓存2 (https://www.dropbox.com/s/8cfund2a2snh4j3/34.C.05%20cc%20normal%20send%20attachement2.sal?dl=0)中显示

4、对于我们的最新产品、我们在尝试发送帧时随机显示 FIFO 下溢错误。 请参阅附件3 (https://www.dropbox.com/s/784a0py70dfkn2u/34.C.05%20cc%20send%20with%20underflow%20attachement3.sal?dl=0)

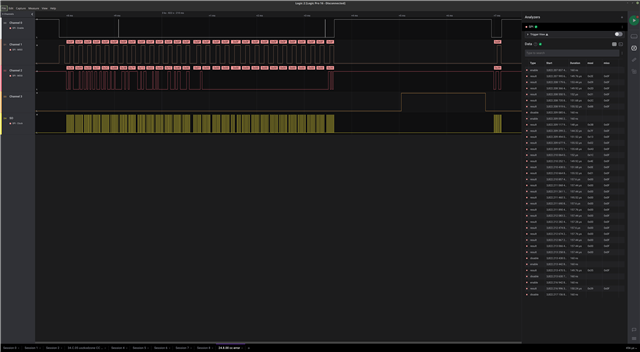

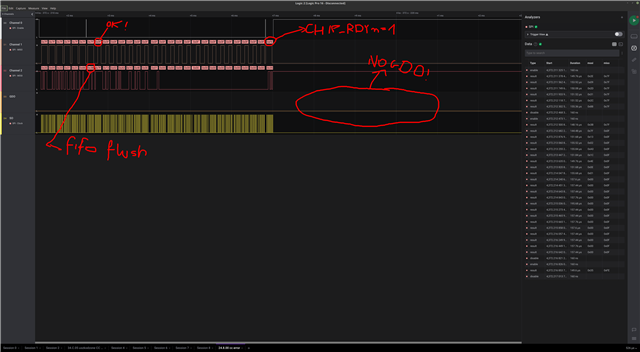

5.在该帧之后,我们尝试发送下一个帧。 我们执行 fifo 刷新、成功并将数据发送到 fifo (状态为0x0F ->确定!!) 在执行 STX 命令时、我们会得到0xFE 状态、指示时钟或电压错误。 GDO 未置位、模块保持在 TX 模式。 启用了加勒比器、模块消耗的恒定电流为35mA。 请参阅附件4 (https://www.dropbox.com/s/vicgmbfnu87butl/34.C.05%20cc%20send%20CHIP_RDYn%201%20attachement4.sal?dl=0)

之后、主 uC 中出现超时、cc115l 复位并重新编程。 复位后、它按预期工作几次发送、并随机返回此问题。 有时在一分钟后、有时在一小时后。 在4小时内、我们在电流 DUT 上有大约8个错误。 目前、我们尚未在每个器件上发现此问题。

什么可能导致问题?

您是否在其他项目中看到过类似的内容?

我们还能提供哪些其他数据?

我们应该测试什么来了解此错误的原因?

我在这里看不到与勘误表相关的信息、但我是否遗漏了一些内容?

此致

Maciej Łaski