首先 , 我的程序使用了CPUtimer定义了一个1ms的运行周期 , 整个程序顺序执行然后等待主中断再循环执行。其中主机还有一个更高优先级的中断是进行高频次的计算,从机则没有这个中断,只有1ms中断。

在此基础之上由于单片资源不足现在需要用到SPI进行两块芯片间的通讯,主从之间会有大概30个16位数据进行交互,期望效果是30个数据每个周期都可以收发一次。我对SPI接收使用了中断且有FIFO,而发送则没有使用中断而是每个周期30个数据采用循环方式发送一组一次,因为我认为发送如果也使用中断一是不能量化一组数据发送的间隔另一个担心会增加中断嵌套的风险。

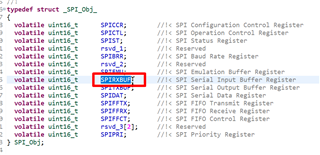

按照我的理解,接收端BUFF里的数据是发送端强制填充进去的,按照数据手册的说法,在RXBUFF被填充满一个16位数据后会生成一个中断,表明数据接收完毕,中断服务函数则将BUFF里面的数据转移到其他地方并清除标志位,等待下一次填充。所以我的理解是接收端是在等待数据的填充,若没有数据的填充则不进行接收数据的转移,在发送端发起数据发送后,随着数据的填充每隔16位一次中断再把数据转移走,这样依次执行直到我30个数据全部发送完毕。

那么问题就来了:

1、我在查看论坛的时候看到文章指出,1M频率下SPI的CLK时钟都在1us,即每收发一位需要1us,一个16位数据就要16us,我发送30个数据所占用的时间就要达到将近500us,这对于一个周期1ms的系统来说是致命的,想要周期性运行这个系统,要么放大周期值要么减少发送的数量。那么在保证1ms前提下有没有什么办法实现我这样的发送需求。

2、由于主机程序内不只一个中断:1ms定时周期中断、高频次计算中断、SPI接收中断。另外两个中断的优先级都高于SPI的中断,那么在从机进行发送期间就会出现这样的情况:

2·1在SPI接收期间,1ms中断或者高频次计算中断产生,若还未接收全16位数据,SPI是会延迟执行抢占的中断等待一个16位数据接收完毕后再去执行抢占还是立即执行抢占?

2·2由于打断了SPI的接收,但是发送端并不知道接收端的接收被打断,发送端持续发送,RXBUFF中的数据是保留已经填充的数据还是呗新的数据替换?

2·3由于高频次计算的中断在执行期间还要消耗一定的时间去进行一些数据的计算,SPI恢复接收将被大大延后,可否在进入中断期间停止CLK信号的产生来让发送端停止发送数据,待抢占中断执行完毕后恢复CLK再继续数据的传输

2·4还是1ms周期的问题,一旦SPI接收被抢占,那么必然无法保证1个1ms周期内30个数据全部收发一次。

综上所述,有没有大佬做过类似的程序,帮我解答一下,助我实现这个功能?