Other Parts Discussed in Thread: TMDSCNCD28388D, DP83822I

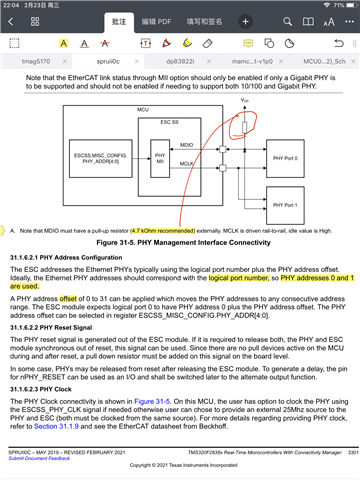

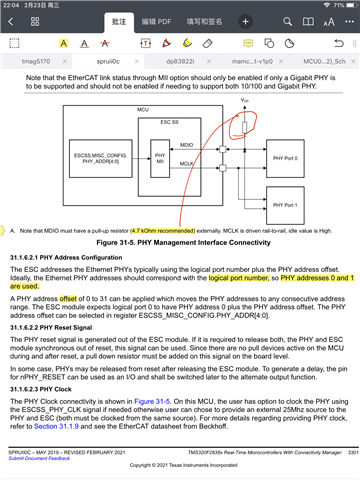

上图为TRM中PHY MDIO上拉电阻的描述 建议4.7K

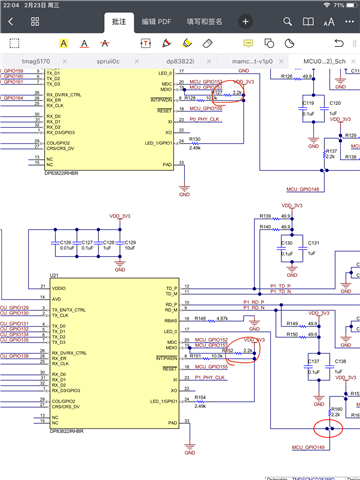

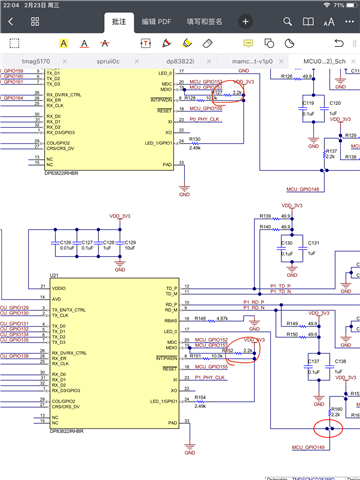

上图为TMDSCNCD28388D EtherCAT部分

Port0 PHY及Port1 PHY的MDIO均设计了2.2K上拉电阻 因此并联的电阻量为1.1K 这是不是上拉太强了呢 这样不会有问题吧

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

上图为TRM中PHY MDIO上拉电阻的描述 建议4.7K

上图为TMDSCNCD28388D EtherCAT部分

Port0 PHY及Port1 PHY的MDIO均设计了2.2K上拉电阻 因此并联的电阻量为1.1K 这是不是上拉太强了呢 这样不会有问题吧

你好,E2E的回复是,DP83822I的数据表上确实要求添加的是2.2K的电阻值。但两个电阻并联并且导致总阻值变小,确实会不正确,两个信号链上应该只有一个2.2K电阻。

较低的总电阻值似乎对F2838x控制卡EtherCAT的使用没有影响,但如果是自制板的话还是推荐按2.2K来设计。

另外这个问题对方已经就这个问题在这款开发板上做记录了。

好的 了解 在我的自制板上 我将标注其中一个2.2K电阻不焊接 感谢帮助