作者:Rick Downs,德州仪器 (TI) 高精度模拟应用工程经理

大多数高精度模数转换器 (ADC) 都没有高阻抗输入。输入信号直接通过一个开关连接到一个采样电容器。这种负载存在一些有趣的挑战。

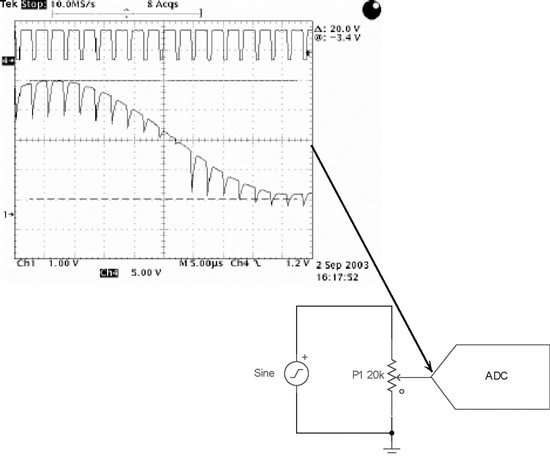

有人试图通过直接连接一个电位计到输入来验证其 ADC 的运行,如图 1 所示。这样做的结果通常让人失望,因为获得的结果并不理想。这种情况下,在 ADC 输入上看到的信号呈现出巨大的峰值,因为大输入阻抗从采样电容器吸取电流,从而导致对电容器充电需要大量的电流。如果在转换器的采集时间 tACQ 内稳定下来,便不会出现问题。但是,如果没有在 tACQ 内稳定到 0.5 最低有效位 (LSB) 以下,则会损耗精度。

图 1 高源阻抗会引起精度损耗

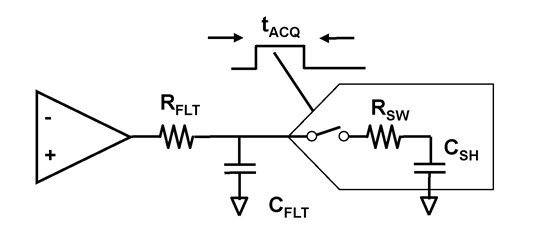

图 2 显示了驱动一个高精度 ADC 的建议电路。CSH 为 ADC 内部的采样电容,而 RSW 为采样开关的导通电阻(通常低到可以忽略不计)。转换器的采集时间 tACQ 期间,采样开关关闭。

图 2 驱动高精度 ADC 的建议电路

外部 CFLT 用于提供充电 CSH 所需的瞬时电流,其必须至少为 20x CSH。一般而言,1nF 较为合适。RFLT 用于阻止驱动运算放大器承受纯电容性负载。这样,RFLT 和 CFLT 构建起一个时间常量为 τ = RFLTCFLT 的 RC 电路。

为了保证所有一切都及时稳定以获得精确的信号采集,tACQ 必须为 ≥ k τ,其中k = ln(2(N+1))。K 为一个 N 位转换器稳定至 0.5LSB 要求的时间常量值。由此,您可以确定最大值 τ,以及 RFLT 的值。

选择驱动运算放大器的关键参数是其单位增益带宽,其必须为 4(1/(2πRFLTCFLT)) 以足够快地稳定。一些设计人员通常会忘记这个要求,可能选择一款比要求慢得多的运算放大器,从而得到令人失望的结果。

如欲了解采样过程、RC 时间常量计算以及正确选择运算放大器的更多详情,敬请访问:

- 《使用 SAR 模数转换器进行马达控制应用中的电流测量》(SBAA081),作者:M. Oljaca 和 J. McEldowney,2002 年 10 月,网址:http://focus.ti.com/lit/an/sbaa081/sbaa081.pdf

- 《设计 SAR ADC 驱动电路,第一部分:ADC 工作原理详解》作者:R. Downs 和 M. Oljaca,2006 年 2 月,网址:http://www.en-genius.net/includes/files/acqt_022106.pdf

- 《ADS8342 SAR ADC 输入》(SBAA127),作者:M. Oljaca 和 B. Mappes,2005 年 1 月,网址:http://focus.ti.com/lit/an/sbaa127/sbaa127.pdf

- 《设计 SAR ADC 驱动电路,第二部分:SAR ADC 输入行为》,作者:R. Downs 和 M. Oljaca,2006 年 10 月:http://www.en-genius.net/includes/files/acqt_100306.pdf

- 《设计 SAR ADC 驱动电路,第三部分:为 SAR ADC 设计优化的输入驱动电路》作者:R. Downs 和 M. Oljaca,2007 年 3 月:http://www.en-genius.net/includes/files/acqt_031207.pdf

- 《外部组件提升了 SAR ADC 精度》,作者:B. Baker 和 M. Oljaca,EDN,2007 年 6 月 7 日,pp 67-75,网址:http://www.edn.com/article/CA6447231.html。

- 《驱动 SAR ADC 首先是选择正确的运算放大器》作者:M. Oljaca 和 B. Baker,EDN,2008 年 10 月 16,pp 43-54,网址: http://www.edn.com/article/CA6602451.html

热门评论

以前对ADC的输入级不怎么注意,都是直接将输入引脚接到被测的电压端或是接RC滤波之后再接到ADC输入端,有的场合出现过情况,有的则没有出现过意外情况。比如之前调试ADS1115的时候直接接到输入脚上就没有任何问题,采回数据特别稳定;而之前调试ADS7811时,就出现了采回数据跳动特别大的情况,用MSP430单片机内部ADC的时候也出现过数据跳动特别大的情况。那时候总结的原因是:慢速ADC牺牲速率…