随着许多公用事业公司将关注焦点转向提升电力系统的质量和效率,他们也正从传统电网向更智能的电网转型。这种转型需要在现有的一次设备基础上添加更多传感器和通信功能,并安装二次设备,如保护继电器、间隔控制器和终端单元,从而保护、控制和监控变电站开关站的一次设备。如下图1所示,二次设备安装在变电站控制室中的面板内。

图1:带保护、控制和监控设备的控制面板

随着更多传感器的连接,数据采集(DAQ)功能对于提高电力系统性能至关重要。DAQ系统需要采集多个模拟输入(电流、电压、温度)的数据,精确处理采集的样本,计算电气参数,并实时地将这些经过处理的参数传送到中心位置进行分析。

用于保护、监控和测量的AC模拟输入具有不同的输入范围、精度和处理要求。为了优化变电站规模,提升测量精度,提高可靠性和安全性,公用事业公司和很多大型企业正从传统仪表变压器向非传统仪表变压器转变,这就需要额外的硬件和处理。由于设备上集成了更多功能,所需的模拟通道数量随之不断增加,算法也变得越来越复杂,计算电气参数的处理要求也越来越高。设计正变得模块化,也变得更基于应用程序,设计人员正在添加模块以增加模拟输入通道的数量,从而降低复杂性。这些添加的模块是出于DAQ系统中所需的功能而配置的,以提高性能并提供可扩展性。

在我们过去发布的题为将多个模数转换器(ADC)连接到单个处理器以实现电网保护和控制的博文中,讨论了接口选择,并提出了将可编程实时单元和工业通信子系统(PRU-ICSS)接口作为优化设计。在此博文中,我们将讨论使用PRU-ICSS将多个ADC连接到单个主处理器的细节、方法和优势。

查看我们的PRU-ICSS参考设计

采用多个ADC且适用于同步相干DAQ的灵活接口(PRU-ICSS)参考设计

采用多个ADC且适用于同步相干DAQ的灵活接口(PRU-ICSS)参考设计

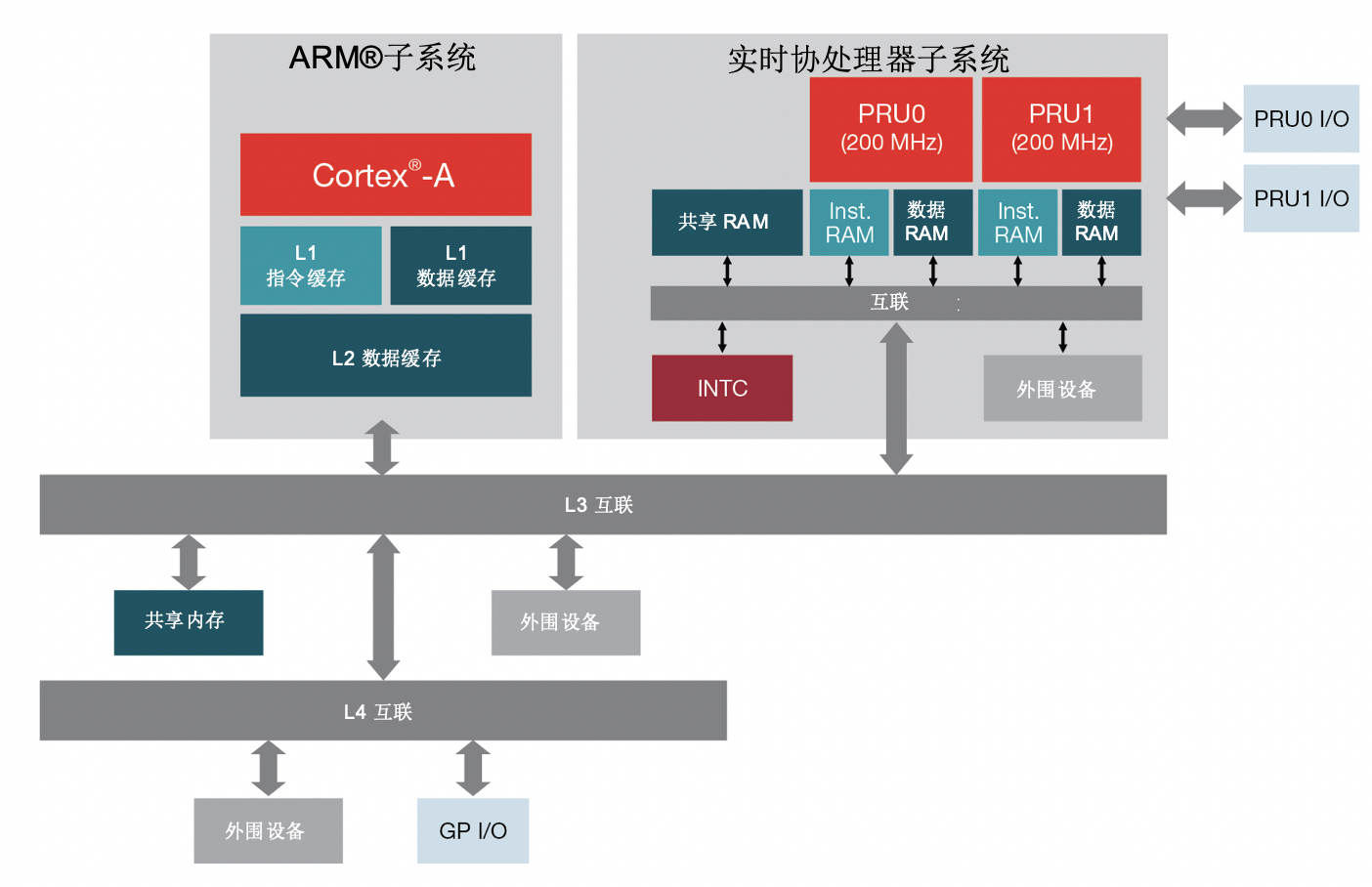

使用PRU-ICSS可以让设计人员更灵活地选择基于采样和处理要求的ADC和处理器。图2是配有实时协处理器的通用内核框图。

图2:配有实时协处理器的通用内核(来源:“确保实时可预测性”第2页)

带有串行外围接口(SPI)的ADC和带有双核PRU-ICSS的主处理器简化了整个系统设计,并提供一个性能提升的成本优化系统。

PRU与Sitara™AM335x、AM437x和AM5x处理器中的ARM®内核一起部署,实现了低延迟、确定性实时子系统的作用。每个PRU子系统包含两个200MHz实时内核(或PRU),每个内核的每个指令周期时间为5ns。不使用带指令管道的实时内核可确保单周期的指令执行。带多位操作指令的PRU小型、确定性指令易于学习和使用。共享内存,和专用于每个实时内核的指令以及数据内存,使所有可能在芯片上构成系统的实时和通用处理器ARM内核之间的程序执行变得灵活。

所用的ADC是一个ADS8688,使用单电源的16位8通道非同步采样多路复用ADC,双极输入电压高达±10.24V,并且集成AFE。它是一个针对低电压或中电压保护、监控和控制应用(包括DTU/FTU)的成本和性能的优化解决方案。在软件中对使用多路复用ADC时观察到的通道间采样延迟进行补偿。ADS8688每个通道的数据吞吐量为500ksps或62.5ksps,满足保护、监控和控制采样要求,而且每个周期可以有60-512个样品。

TI的采用多个ADC且适用于同步相干DAQ的灵活接口(PRU-ICSS)参考设计提供了ADS8688和主处理器AM335X之间的接口,从而捕获数据并执行相干采样。参考设计还具有以下三个关键优势:

- 可扩展性/灵活性:可连接多个ADS8688 16位ADC(6)和带SPI和独立可控芯片选择的48个模拟输入通道。

- 性能:通过动态调整计时来实现相干采样,以从ADC中获取高AC性能。

- 集成:通过在DAQ系统、工业以太网接口、信号处理和用户界面上使用单处理器,降低了形状系数和成本。

PRU-ICSS采用了一个增强的通用输入/输出(GPIO)模块,支持直接输入和直接输出模式。PRU核寄存器R30用作通用输出的接口,寄存器R31用作输入的接口。写入PRU核的寄存器R30的任何值将在一个周期后输出到PRU的外部引脚(R30位0对应引脚0,位1对应引脚1,依此类推)。

相反,每当PRU核读取寄存器R31时,PRU核外部引脚上的值将在一个周期后存储。引脚0的值存储在R31位0中,引脚1存储在R31位1中,依此类推。除了直接输入和输出模式,PRU的确定性使其非常适合执行与多个ADC通信的同步SPI端口。

PRU-ICSS中的GPIO管脚在所有ADC和处理器之间传输数据。当PRU-1处理外部数据通信时,PRU-0执行低级过滤和零交叉检测。运行实时Linux®的ARM内核可以进行数据、通信和人机界面(HMI)控制的进一步处理。

为了使用PRU-ICSS实现DAQ系统,所有ADC都被配置为同时采样相同的通道。参考设计突出了PRU-ICSS通过每个线周期采集640个样本来处理1536KSPS数据速率(每个样本=16位)的能力。对于50Hz周期,这相当于同时通过6个ADC的每个信道32KSPS(640样本/周期 * 50Hz * 6 ADCs * 8多路复用通道 = 1,536KSPS)。第二个PRU后处理数据以实现相干采样。

PRU-ICSS为6个TI ADS8688 ADC提供了简化的同步接口,能够灵活地通过在指定范围内根据输入信号频率改变芯片选择计时来调整采样率。数据可以从所有ADC中捕获并实时处理。同步SPI数据处理发生在PRU-ICSS中的两个PRU核中,释放另一个PRU核来为输入的信号频率提供反馈回路(调整ADC采样率以实现相干采样),同时对输入的ADC数据执行低级筛选。使用PRU-ICSS进行模拟信号捕获和处理可减少处理器开销,并允许执行外部通信协议和图形显示。

其他资源

- 观看培训视频,“PRU-ICSS:用多个ADC连接处理器”

- 阅读博文,“电网基础设施与Sitara处理器的模拟连接”