Other Parts Discussed in Thread: OPA376

最近比较忙,把这个主题中断了,现在利用周末的时间,把这个主题继续下去。希望本月能把运放基本参数这一主题结贴。并开始新的主题。

今天用一个贴子写两个关于运放输出特性的小主题,一个是Rail-Rail 输出,另一个是输入短路电流。

先说轨至轨输出(rail to rail output)。现在在低电压运放的中,很多都是轨至轨输出。运放的轨至轨输出是由MOS作输出级设计实现的。早期的运算放大器输出级是带有NPN电流源或下拉电阻的NPN射极跟随器。这种使用BJT的互补共射极输出级无法完全摆动到电源轨,只能摆动到电源轨的晶体管饱和电压CESAT范围内。对于较小的负载电流(小于100 µA ),饱和电压可能低至5至10 mV;但是,对于较高负载电流,饱和电压可能增加至数百毫伏

轨至轨输出的本意是指,运放的输出电压可以达到电源轨。但实际是它是十分接近电源轨。只说这么一个定义是没有多大意义的。下面要说一下这里关于轨至轨输出的一些需要注意的问题。

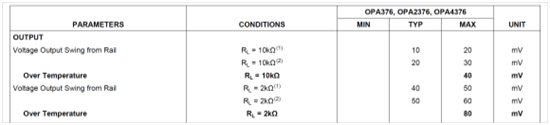

先看下图,是OPA376的datasheet上的数据。看到在不同负载下的输出离电源轨的电压值是不同的。

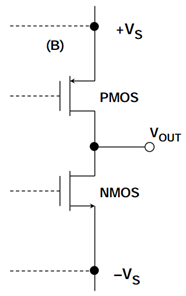

这是由于采用CMOS FET构建的输出级(如下图)可以提供近乎真正轨到轨的性能,但只是在空载条件下。如果运算放大器输出必须流出或吸入相当大的电流,则输出电压摆幅会降低,降幅为FET 内部导通电阻上的I×R 压降。一般而言,精密放大器的导通电阻在100 Ω 左右,但高电流驱动CMOS 放大器的导通电阻可能小于10 Ω。这就是引起输入不能完全达到电源轨的根本原因。

另一方面,运放的输出信号到轨的电压值,随温度而变化。这同样可以在OPA376的datasheet中的表格中看到,并且在全温范围内,一般会出现在高温的情况,输出信号到轨的电压值会变大。这是由于MOS导通电阻,具有正温度系数,温度越高,导通电阻越大。这也就是造成了全温范围内压差VSAT = VS – VOUT会变大。

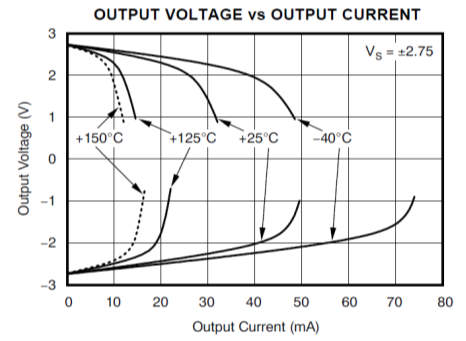

下面引出一张图表,这张图表在运放的datasheet中非常常见,但也经常被忽略,它反应了一个重要结论:随着温度的上升,和输出电流的上升,运放输出信号与电源轨的压差VSAT = VS – VOUT也随之增大。原因正如上面所解释的。当然还有一个问题,当输出电压越接近电源轨时,信号的失真会变的差一点。因此没有真正能达到电源轨输出的运放。根据上面的原因,离电源轨远一点,更容易达到高的信号质量。