TPA3116的数据手册 7.3.7节提到:

The impedance seen at the inputs should be limeted to an RC time constant of 1ms or less if possible.

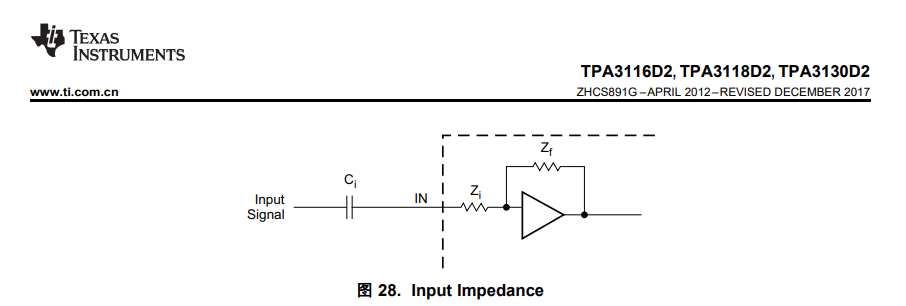

请问从输入看到的阻抗指的是什么,是从芯片音频输入引脚向芯片内部看,还是向外部看?

手册上提到芯片音频输入端的输入电阻是随 增益的变化而改变的。RC的R就是输入电阻,C就是隔直的电容吗?

如果是这样,Table2 Recommanded input AC-Coupling Capacitors中的,RC都是90ms左右,感觉不对劲啊。