工具/软件:Code Composer Studio

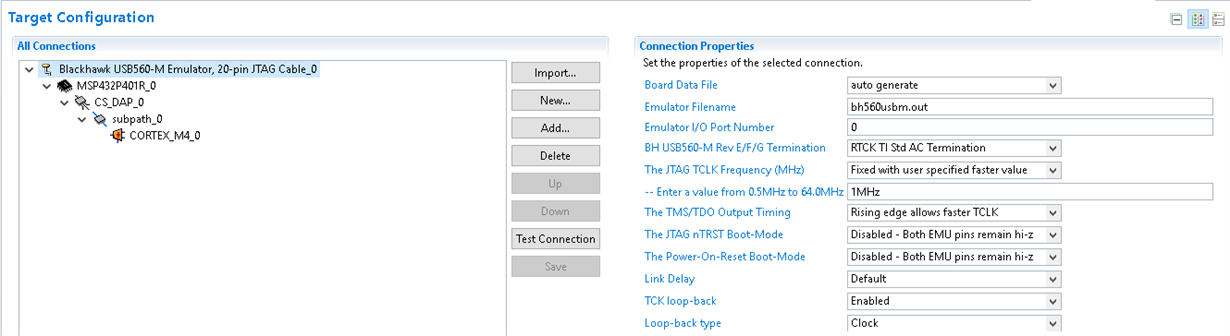

当使用 Blackhawk USB560-M 仿真器时、20引脚 JTAG 电缆连接到不在 JTAG 连接器上回路 TCLK 的目标(即在目标配置中必须启用 TCK 回路)、 发现必须将 JTAG 输出时序设置为“上升沿允许更快的 TCLK”以允许目标连接。

例如、在创建一个新的目标配置后、JTAG 输出时序缺省为"下降沿为 JTAG 标准":

测试连接失败:

[开始:Blackhawk USB560-M 仿真器、20引脚 JTAG Cable_0] 执行以下命令: %CCS_base%/common/uscif/dbgjtag.exe -f %boarddatafil文件%-RV -o -F inform、logfile=yes -S pathlength -S integrity [结果] --- [打印电路板配置路径名]--------------- C:\Users\MR_HAL~1\AppData\Local\TEXASI~1\ CCS\ccs720\0\0\BrdDat\testBoard.dat -- [打印重置命令软件日志文件]----------------- 此实用程序已选择了560/2xx 类产品。 此实用程序将加载程序'bh560usbm.out'。 库构建日期为"2017年23日"。 库构建时间为'18:28:03'。 库软件包版本为'6.0.628.3'。 库组件版本为'35.0.0'。 控制器使用可编程 FPGA。 旧的 VHDL 代码的版本号为"0"(0x00000000)。 新的 VHDL 代码的版本号为'386336272'(0x17070610)。 控制器的版本号为'6'(0x00000006)。 控制器的插入长度为"0"(0x00000000)。 CABLE + POD 的版本号为'6'(0x00000006)。 CABLE + POD 的功能编号为"0"(0x00000000)。 此实用程序将尝试重置控制器。 此实用程序已成功重置控制器。 ---- [打印重置命令硬件日志文件]----------------- 扫描路径将通过切换 JTAG TRST 信号进行复位。 控制器是 Nano-TBC VHDL。 该链路是560类 D 型多用途电缆。 该软件配置为具有 Nano-TBC VHDL 功能。 控制器将通过其寄存器进行软件复位。 控制器在其 EMU[0]输入引脚上有一个逻辑零。 控制器在其 EMU[1]输入引脚上有一个逻辑零。 控制器将在输出引脚上使用下降沿计时。 控制器无法控制输入引脚上的时序。 扫描路径链路延迟已精确设置为"2"(0x0002)。 实用程序逻辑之前未检测到功率损耗。 实用程序逻辑当前未检测到功率损耗。 硬打开控制器时出错。 ---- [发生了错误,该实用程序已中止]----- 此错误由 TI 的 USCIF 驱动程序或实用程序生成。 值为'-230'(0xffffff1a)。 标题为"SC_ERR_PATH_measure"。 解释是: 测得的 JTAG IR 和 DR 扫描路径长度无效。 这表示链路延迟或扫描路径中存在错误。 [结束:Blackhawk USB560-M 仿真器、20引脚 JTAG Cable_0]

尝试启动调试会话失败的条件为:

[引用]CS_DAP_0:连接到目标时出错:(错误-230 @ 0x0)测得的 JTAG IR 和 DR 扫描路径长度无效。 这表示链路延迟或扫描路径中存在错误。 (仿真软件包6.0.628.3)[/QUERP]

通过查看具有 LSA 的 JTAG 信号可以看出、由 Blackhawk USB560-M 驱动的 TMS 和 TDI 信号在 TCLK 的上升沿发生变化、而由目标驱动的 TDO 信号在 TCLK 的下降沿发生变化:

当目标配置中的输出时序被更改为"上升沿允许更快的 TCLK"时、测试配置通过并且能够调试目标:

通过查看具有 LSA 的 JTAG 信号可以看出、由 Blackhawk USB560-M 驱动的 TMS 和 TDI 信号在 TCLK 的下降沿发生变化、目标驱动的 TDO 信号也是如此:

上面所示的是在 Windows 10下运行的 CCS 7.2.0.00013、其中包含 Blackhawk 仿真器6.0.83.003和 TI 仿真器6.0.628.3。

因此、在 CCS 软件或 Blackhawk USB560-M 固件中、某些东西会导致仿真器 TMS 和 TDI 输出在 TCLK 的不同边沿上发生变化、而不是在 CCS 目标配置文件中指定的边沿上发生变化。 由于这会导致尝试创建目标连接时出现故障、因此可以调查反转的原因吗?