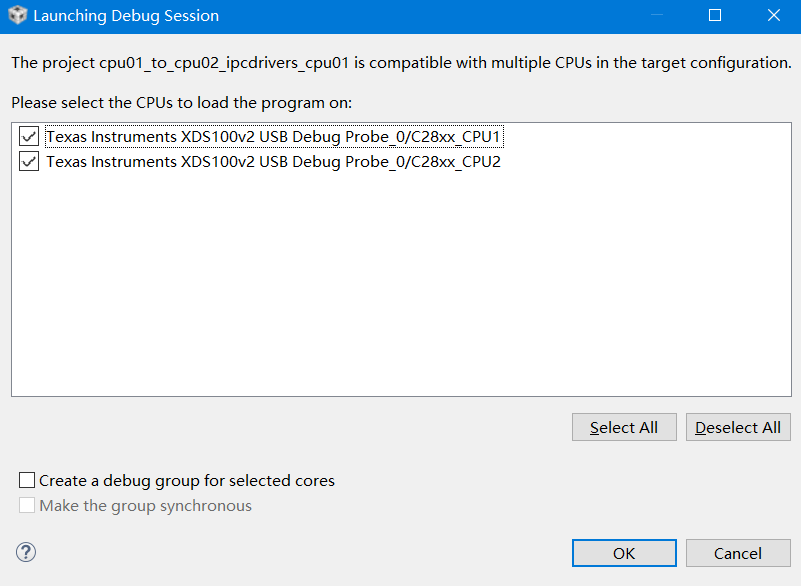

在使用controlsuit里面的controlSUITE\device_support\F2837xD\v210\F2837xD_examples_Dual\blinky_dc文件夹里面的例程,把CPU1和CPU2都导入了,build后选定CPU1的那个工程,点击Debug,然后在下面弹窗时全都勾选上了,烧录... ...

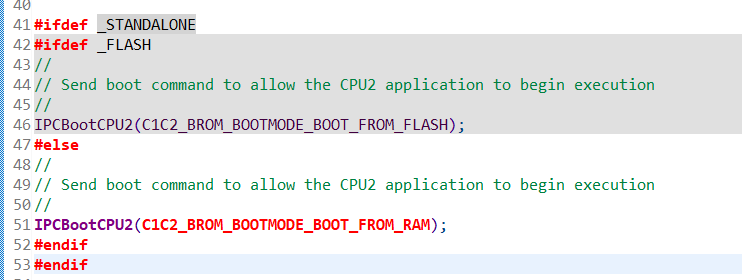

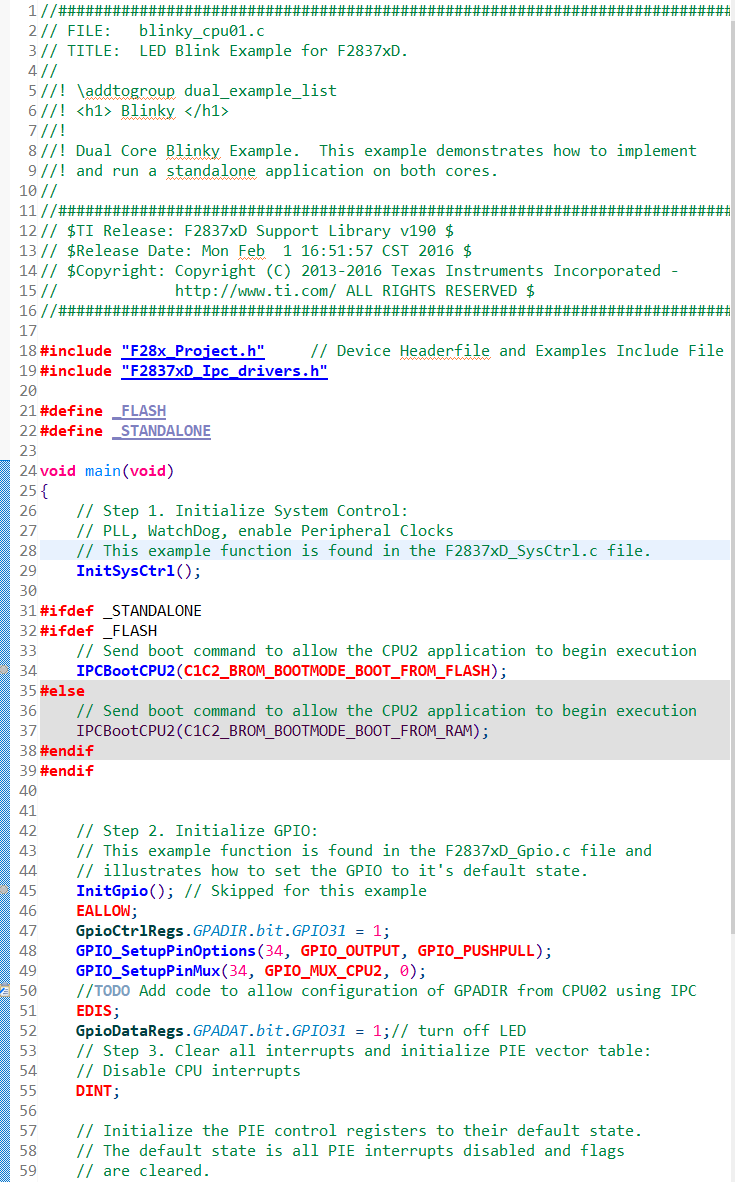

在cpu1那个程序中,我为了让CPU1来控制启动CPU2,就添加了一个宏定义,启用了IPCBootCPU2(C1C2_BROM_BOOTMODE_BOOT_FROM_RAM)这个函数

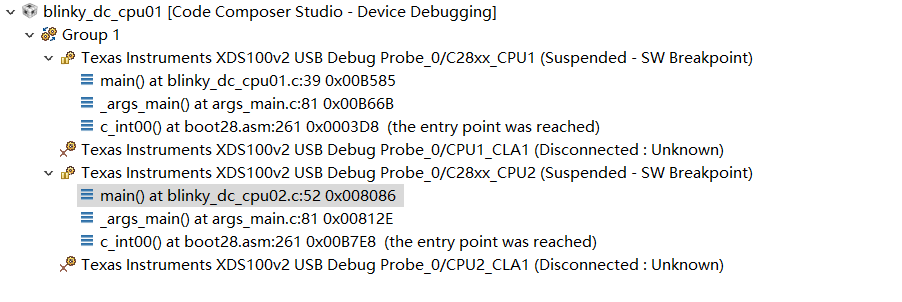

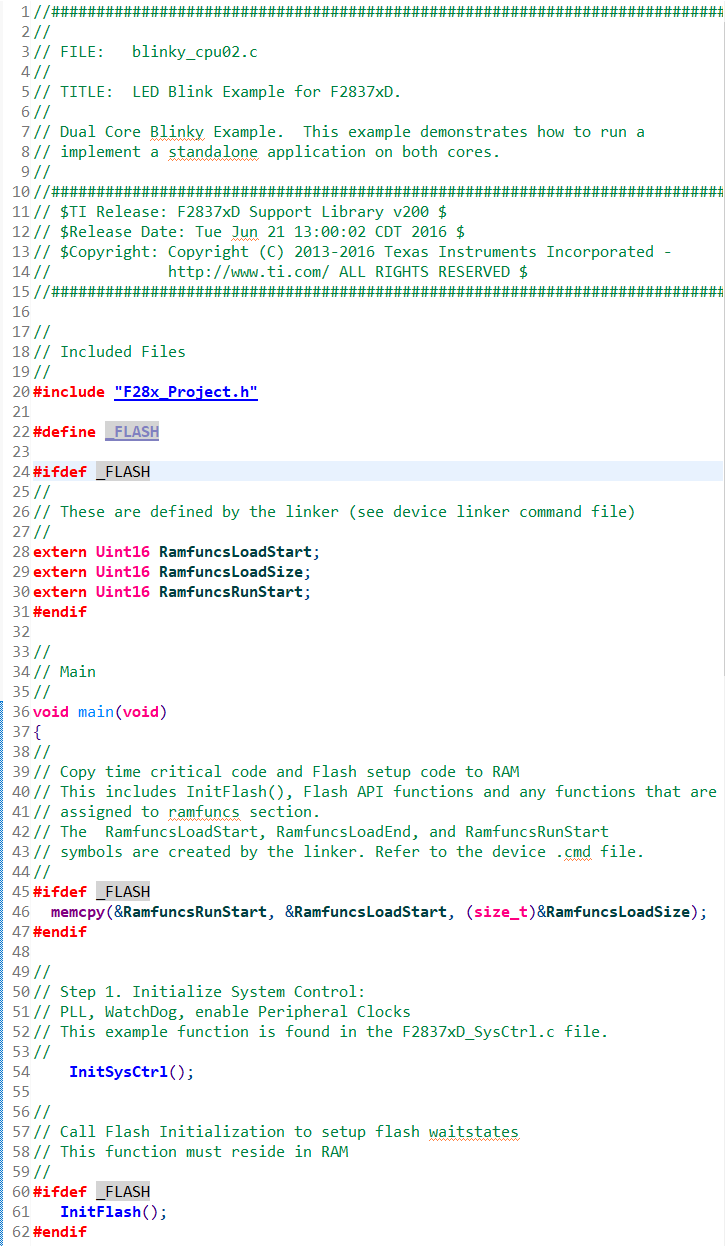

然后cpu2借鉴C28x_Microcontroller_ODW_2-0.pdf中的步骤给烧进去cpu2配套的程序了

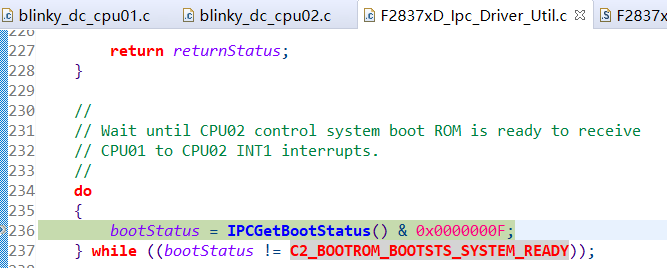

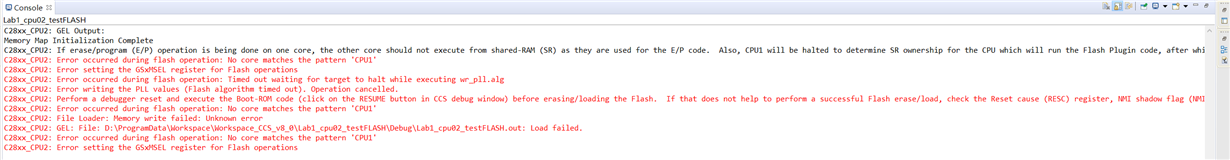

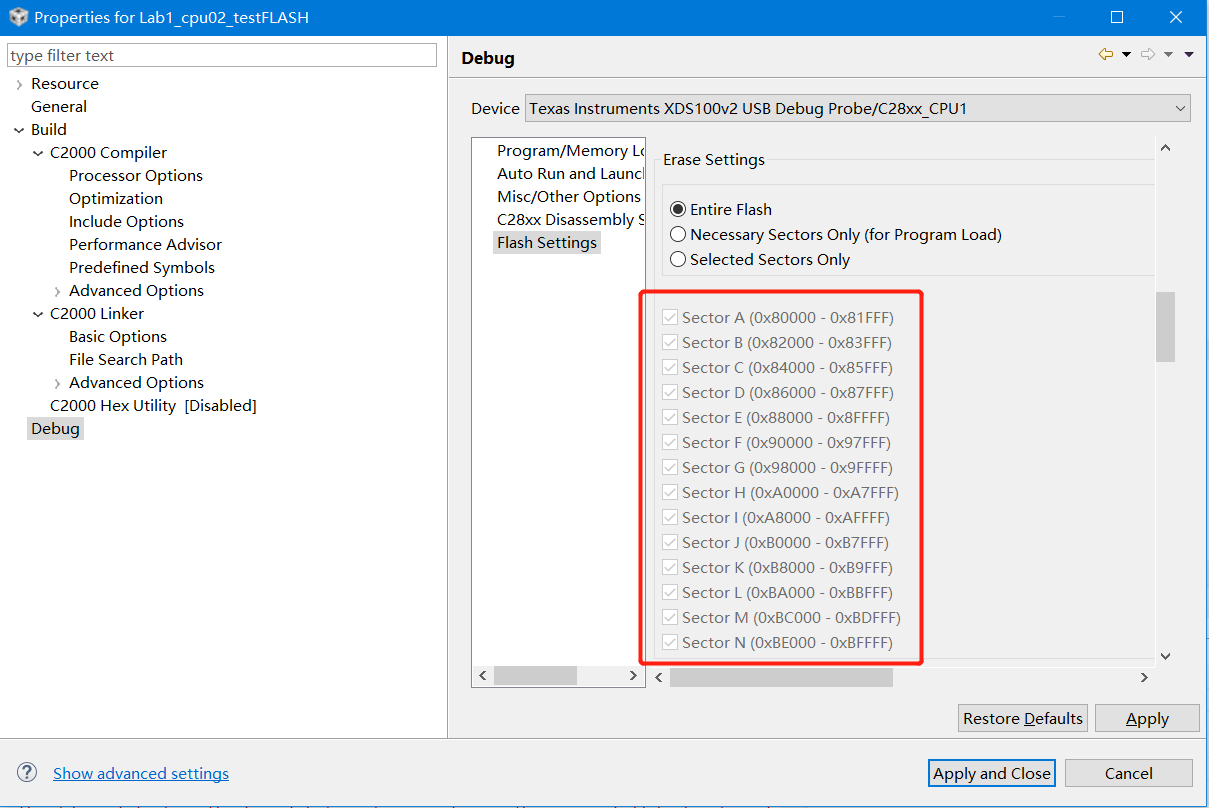

但这时选定cpu1,run起来后卡到这里了:

bootStatus的值为0,也就是说CPU2并没有被CPU1给控制启动了,这个为什么会卡到这里呢?到底应该如何做才能让CPU1控制启动CPU2呢,而不是采用C28x_Microcontroller_ODW_2-0.pdf里面的方式,分别启动CPU。