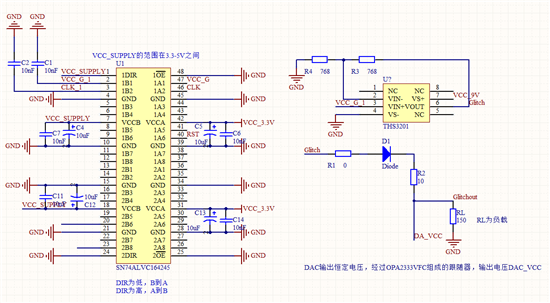

首先,输入说明:VCC_G为FPGA产生500MHz的方波信号,希望此信号通过CFB后,不改变原信号的rise time和频率。电路图为下图所示,其中VCC_SUPPLY为3.3V。RL为150Ω的负载,需要保证负载上的电流最小30mA,最大无限制。DA_VCC的加入是抬高方波信号低电平的值,DA_VCC最大的值不会超过高电平的值。

问题①:SN74ALVC164245的A端和B端电压是否在一个范围内连续可调?datasheet上B的电压3.3V 5V是否是在3.3V到5V的范围内随意给一个电压都OK?这个问题是否要我转到时钟页面提问。

问题②:我现在在THS3201输出端测得的信号完全不是我想要的波形,请问具体在哪里链接有问题?所测得的波形与下图类似,(不是原图)

问题③:若我去掉D1,OPA2333输出的电流是否会倒流入R1支路?

是否有更好的办法抬高Glitchout部分的方波信号的低电平?

非常感谢