为CODEC和ADC配置PLL或时钟方案似乎是一项艰巨的任务。由于PLL的设计是为了接受广泛的输入时钟,无论是常见的还是不常见的,有很多方法来配置它,这样做很容易迷失方向。这就是为什么我们有一个PLL CODEC/ADC Calculator,帮助您确认您的PLL配置!

Audio CODEC/ADC PLL Calculator可以在这里找到:

要开始使用这个工具,里面有一个Table of Contents,它提供了设备系列及其各自的PLL/Clock calculator链接,你只需选择你需要的系列,它会带你到适当的计算器使用。例如,如果选择TLV320AIC310x链接,则会转到下一页:

在这里,你可以输入不同的锁相环系数或检查你已经产生结果。此工作表中有允许您输入信息的不同块以及提供值的块(如Fsref和check约束)。

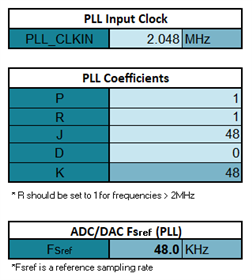

如果提供2.048MHz的输入时钟,可以在PLL Input Clock块中输入该值。下一步是改变PLL系数块中的P、R、J和D系数,该PLL系数块将把输入时钟分频为期望Fsref 48khz。使用P=1、R=1、J=48和D=0将产生48kHz的Fsref。您可以通过查看ADC/DAC Fsref(PLL)块来确认这一点。

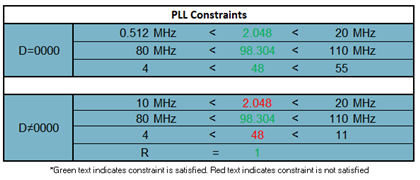

在使用PLL时,还需要遵循一些限制条件。这些约束可以在设备数据手册的适当部分找到,但也包括在计算器页的PLL Constraints块中。在这里,您可以看到基于所选择的PLL系数是否满足约束。绿色文本表示满足约束,红色文本表示不满足约束。

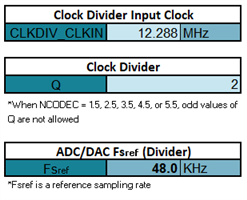

如果您有一个44.1kHz或48kHz的整数倍,您不需要锁相环,可以使用时钟分频器来简单地划分输入时钟。这可以通过使用Clock Divider Input Clock和Clock Divider块来实现。生成的Fsref显示在ADC/DAC Fsref (Divider)块中。

在PLL/Clock Calculator 中包含一些额外的信息,例如编程PLL系数所需的Register Information 和Audio Clock Generation 框图。PLL系数的Register Information 显示用于配置系数的页、寄存器和位。Audio Clock Generation 框图有助于直观地看到您正在生成什么以及如何使用不同的输入时钟。