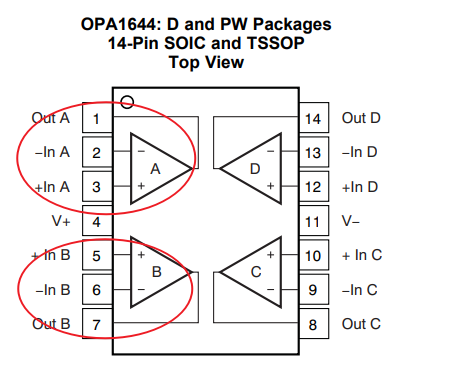

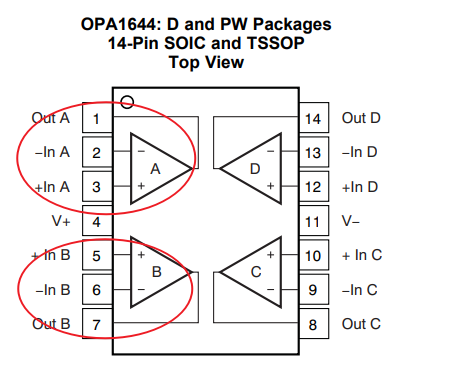

实测发现A通道的输出会耦合到B通道中。

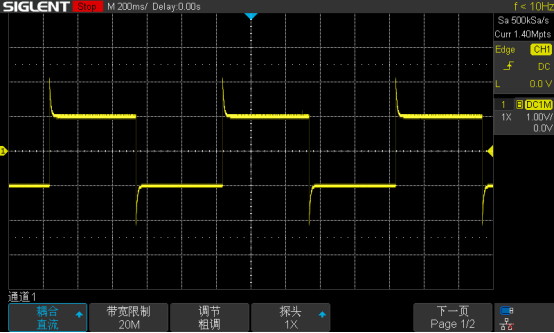

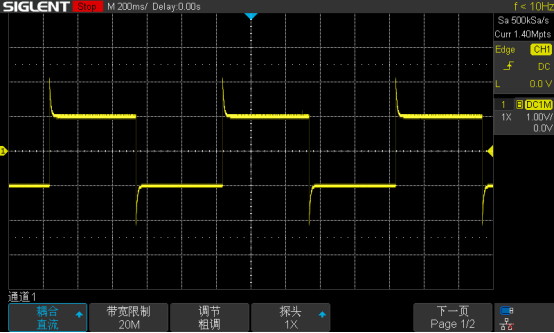

这是A通道的输出波形图; 芯片供电为正负4.5V

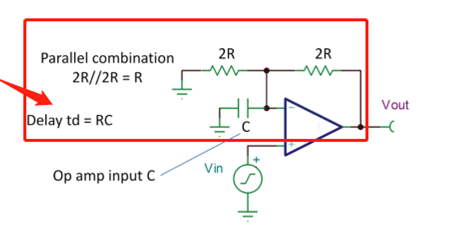

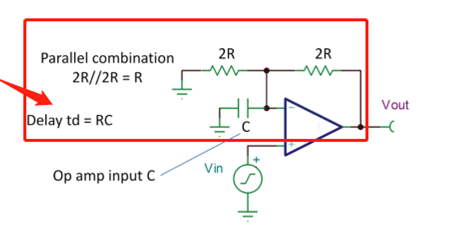

其中输入的信号源为频率1Hz,幅度为1V的波形,毛刺来自寄生电容C

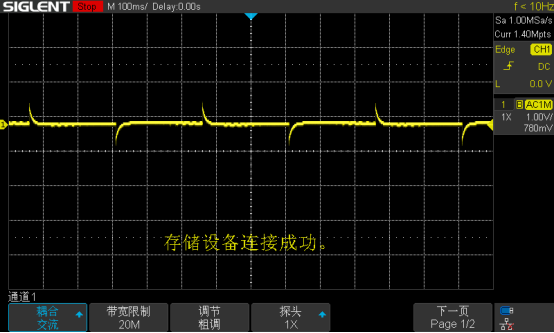

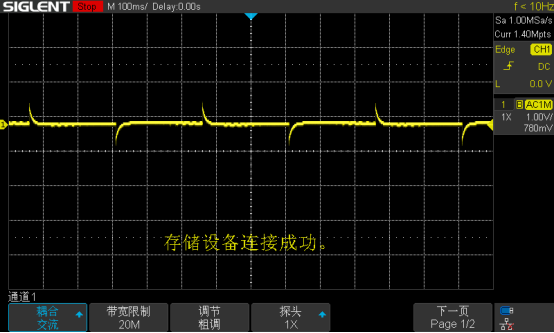

这是B通道的输出端测量的波形

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

实测发现A通道的输出会耦合到B通道中。

这是A通道的输出波形图; 芯片供电为正负4.5V

其中输入的信号源为频率1Hz,幅度为1V的波形,毛刺来自寄生电容C

这是B通道的输出端测量的波形

您好,这四个通道,只使用了两个通道,还是只是用了A通道?不用的通道是如何处理的?

感谢您的反馈,针对layout,我简单列举几点:

1.电源的高频去耦电容比如0.1uF或者0.1nF尽量靠近电源端(尽量小于0.25inch),保持地平面和电源平面远离IO引脚,避免产生更多的寄生电容,IO口的寄生电容很容易引起器件的不稳定性。

2.接地线和电源线避免太窄,这样可以减少引脚和去耦电容间的电感,滤除低频的去耦电容 可以放置在距离器件稍微远的地方。

3.尽量缩短输入走线。输入走线尽量远离电源线和输出线,更大程度上减少寄生耦合。