Part Number: CDCE72010

Hi TI,

Please help to double check CDCE72010 setup issue.

Issue:

Using CDCE72010 as Clock Synchronizer, but failed on the PLL lock stage by watching PLL_lock pin status.

Setup:

1) using primary clk, lvds mode, 100MHZ

2) using VCO, LVPECL mode,1000MHz

3) try different M/N/feedback/refclk divider, keep ratio is 10:1, and try different Icp, try output frequency:100MHZ/200MHZ/1GHz, no pll lock

Setting:

REG0=82300270

REG1=01860021

REG2=68400002

REG3=83400003

REG4=68800004

REG5=68800005

REG6=68080006

REG7=68080007

REG8=690e0098

REG9=eb000c09

REG10=004c063A

REG11=0000268B

REG12=0000180C

Phenomenon:

1) configure Lock-Detect Window (Register 7 Bits [1:0] and Register 9 Bits [7:6]) to reserved status, PLL_lock pin is high, but pll output clk and reference clk phase don't have fixed phase offset.

2) configure Lock-Detect Window (Register 7 Bits [1:0] and Register 9 Bits [7:6]) to other phase offset value, PLL_lock pin is low.

3) although PLL lock is failed, but output clk frequency is correct and has good performance, but has unstable phase, as shown in fig 2.

4) read 0x0c register value is 0x60009b0c

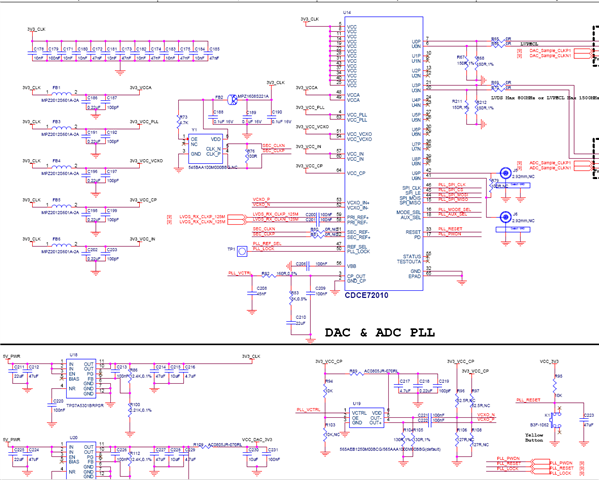

Schematic is shown in fig.1

Fig1

Fig2