Other Parts Discussed in Thread: LMK00334

这种pcie CLK buffer需不需加耦合电容,为什么输出信号只有一个,且电平被拉高,还有一路没有输出

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

这种pcie CLK buffer需不需加耦合电容,为什么输出信号只有一个,且电平被拉高,还有一路没有输出

您好,VAC_REF 接的R16是不是悬空,没接,这个引脚在VCC小于3V的时候直接悬空。

另外,输入输出我看您都是DC耦合的,输入是什么信号,是否满足CDCLVP1102的Vih和Vil要求。

因为CDCLVP1102主要是LVPECL, LVDS,LVCMOS/LVTTL这几种电平的buffer,PCIE的buffer我建议使用LMK00334,它是一款专门PCIE clock buffer。

https://www.ti.com.cn/product/cn/LMK00334?keyMatch=LMK00334&tisearch=search-everything&usecase=GPN

我的VCC 是3.3V 那VAC_REF 是不是也要接3.3V;输入的信号 是什么类型的不是很清楚,只知道是 差分的 PCIe标准的时钟;LMK00334这个IC 我看了一下好多路用不到有些浪费。现有这个CDCLVP1102有没有办法调好,输入一个PCIE 的clk,得到两上PCIEclk 分别给两个设备用;或者这个PCIE clk可以不用缓冲器么直接用电阻分再加一个电容耦合。

VAC_REF是输入LVPECL信号的偏置电压,它的范围是VCC-1.6V~Vcc-1.1V。

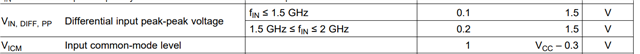

PCIE是HSCL电平,对于CDCLVP1102来说,它要求的差分输入电压范围以及共模电压如下。您看下您的clock信号差分电压是否满足下面要求?

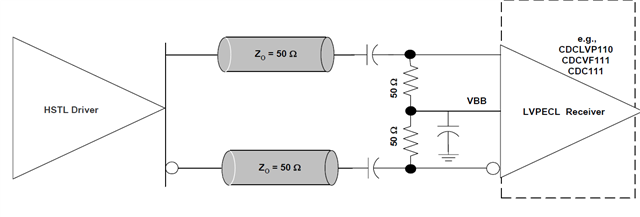

如果差分电压幅值符合要求,由于HSCL和LVPECL的共模电压不同,所以需要使用AC耦合。因为一般都是推荐客户直接使用PCIE的clock buffer,如果使用CDCLVP1102,就需要重新建立新的共模电压。

参考下面HSTLL和LVPECL的耦合方法,将VAC_REF替换到下面电路中的VBB。 按照这样修改电路试试看,能够解决您的问题。 如果不能的话,建议使用LMK00334这类PCIE clock buffer。