Part Number: CDCLVC1310

设计原理图如下:我连接OE,IN_SEL0到3.3V,IN_SEL1到gnd,输出sec_inn输入的时钟,可以吗?输入时钟频率为50MHz,幅度1.12-2.36v

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: CDCLVC1310

设计原理图如下:我连接OE,IN_SEL0到3.3V,IN_SEL1到gnd,输出sec_inn输入的时钟,可以吗?输入时钟频率为50MHz,幅度1.12-2.36v

您好,

我连接OE,IN_SEL0到3.3V,IN_SEL1到gnd,输出sec_inn输入的时钟,可以吗?

VDD和VDDO都是3.3V供电,因此上述连接是可以的;

输入时钟频率为50MHz,幅度1.12-2.36v

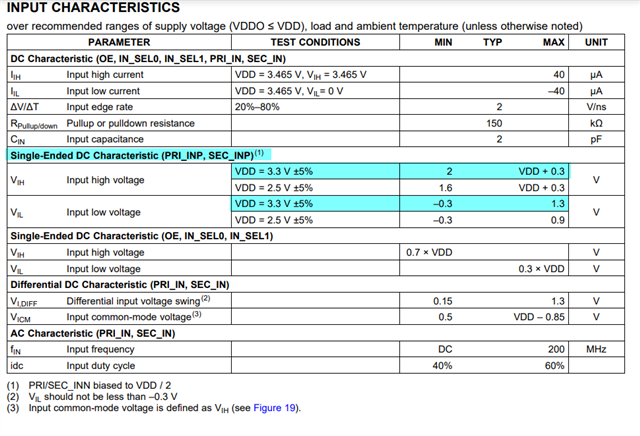

输入时钟频率50MHz没问题,看您电路图中是单端输入,因此需满足下面截图输入规格,即最小高电平是2V,最大低电平是1.3V。您这里描述的“幅度1.12-2.36v”是指低电平1.12V,高电平2.36V吗?如果是的话,那么是可以的。

不使用的XTAL连接没问题;

不使用的PRI_IN输入可以悬空,因为内部已经有偏置;

单端输入的话,应输入SEC_INP同向输入端,反向输入端可以悬空;

不使用的输出悬空,没问题;