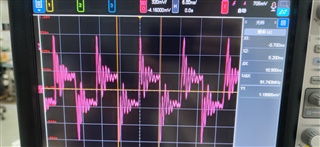

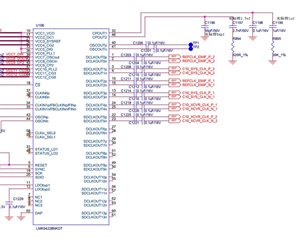

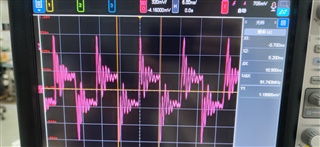

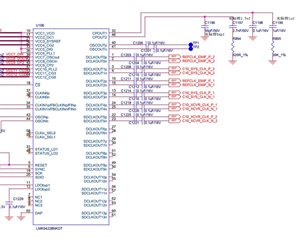

你好,这是我在LMK04228芯片输出0.1uF电容后端,用差分探头测量到波形,发现这个波形存在类似震荡的现象,导致FPGA端无法锁定时钟信号。

请帮我们分析一下存在的问题和原因,谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好,这是我在LMK04228芯片输出0.1uF电容后端,用差分探头测量到波形,发现这个波形存在类似震荡的现象,导致FPGA端无法锁定时钟信号。

请帮我们分析一下存在的问题和原因,谢谢。

您好测试的时候先测量LMK04228的输出端,也就是还没经过AC耦合电容的信号,看是否稳定?

另外,您这是配置的了LVDS输出还是LVPECL输出?每个通道输出波形都是这样的吗?

如果配置的是LVDS输出,那么在靠近FPGA输入端在差分信号PN之间端接100ohm电阻再测量下。

其次引起这种振荡的原因就是考虑layout了,差分信号是否尽量走的等宽等间距?