Other Parts Discussed in Thread: PLLATINUMSIM-SW, LMX2594

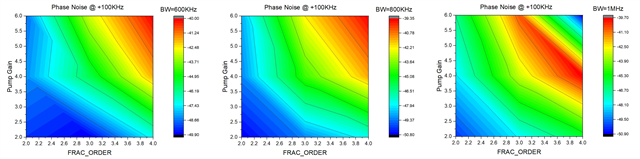

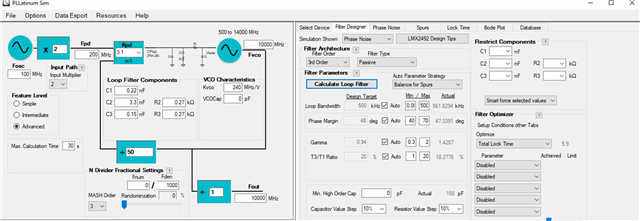

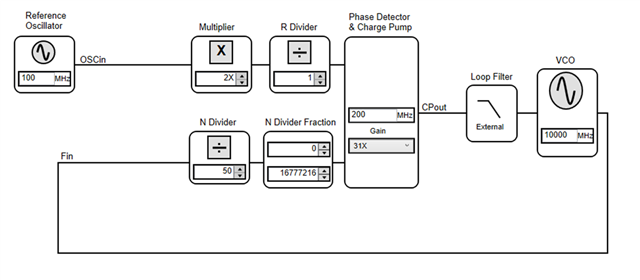

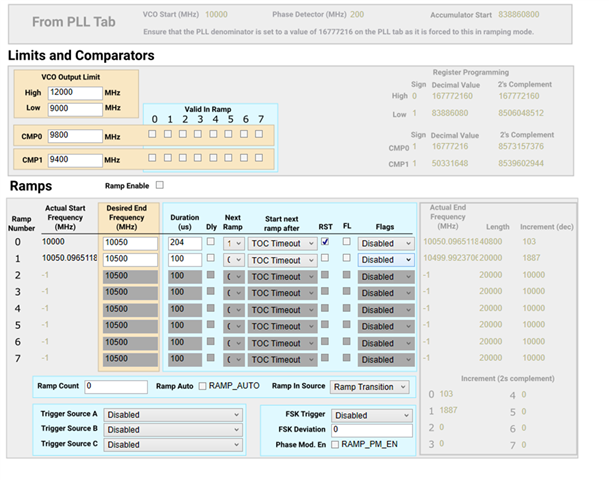

For Chirp signal genenrated by LMX2492+CHC2442, frequency .vs. time Chirp Linearity is critical for our application. However, Suggested by some experience, the actul generated Chirp Linearity quality would be affected by Loop filter configuration and Charge Pump Gain , by the same Loop filter configuration, Chirp Linearity would be better with higher Charge Pump Gain, but phase noise would be accordingly degraded. we also have several Chirp Ramping segments tried, but it seems no obvious Linearity improvement on Chirp signal with a time interval of 204us and a bandwidth of 50MHz. TI official PLL design tool of "TICS Pro" is effective for single CW frequency locking configuration, but we have no idea on how to improve Chirp Linearity with it. Considering Chirp Linearity could be the transcient responses, the design guidance is missing for the best Chirp Linearity quality achievment. so would you please present us the guidance on Chirp Linearity improvement with better phase noise simultanouly, it should inculde Loop filter configuration, Charge Pump Gain, chirp raming segments and other factors not mentioned. it is very hopefully to be effective. very looking forwardws to your prompt reply. Thanks!