按照官方开发板原理图做了实验板,具体为ths4521+ads1278,基准电源用REF5025+opa350。

采用高精度模式,spi、TDM、FIX模式,clk为100kHz。

看资料只提到高精度模式下clk最大为27mHz,那么请问clk最小有限制?

因为实验板遇到如下问题:

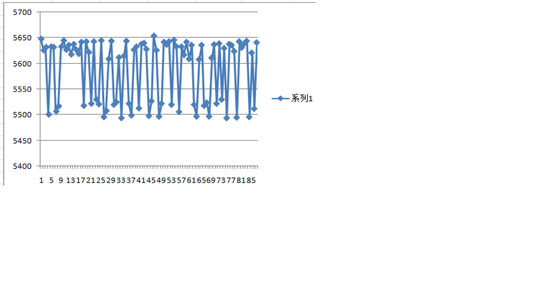

1.将THS4521的输入端短接到地,采集到数据有约40uv的跳变,跳变太大。

2.接上传感器,传感器阻抗为390欧姆,采集到数据有约150uv的跳变,跳变更大,感觉阻抗匹配不是很好。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

要说CLK和SCLK的关系,可以看下数据手册Page9的帧同步时序,CLK的下降沿到SCLK的下降沿的时间tcs的范围。