以上是我的应用场景:通过CDCE62005提供DAC5682Z的工作时钟和FPGA的工作时钟;CLK0和CLK1都是200MHz的时钟,在FPGA内部使用DDS IP核生成一个20MHz的正弦信号,通过DDR接口传递给DAC5682Z作为两个通道的数据;CLK2也是200MHz,DDR接口上升沿和下降沿发送的都是同样的数据;

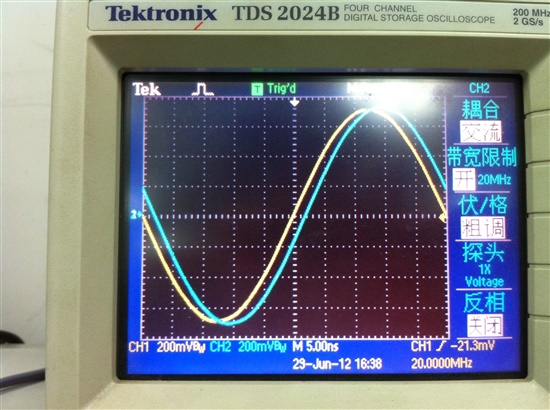

DAC5682Z配置为内插2倍模式,通过示波器观察两个通道的输出,发现两个通道有2.5ns左右的相位差异,如下图所示:

请问这个相差是在哪里产生的呢?如果减小或者消除,在我的应用环境中需要两通道的输出相差小于等于50ps,DAC5682芯片能否达到这个指标呢?