Other Parts Discussed in Thread: LMK04828

ADC12DJ3200工作在JMODE2模式,采样率3G,sysref为10M,时钟由lmk04828提供,接收端为FPGA,adc的配置如下:

ADD_STEP1 = 16'h0000,REG_STEP1 = 8'hB0, //soft reset

wait 200ms

ADD_STEP2 = 16'h0200, REG_STEP2 = 8'h00, //JESD_EN DISABLE

ADD_STEP3 = 16'h0061, REG_STEP3 = 8'h00, //CAL_EN DISABLE

ADD_STEP4 = 16'h0201, REG_STEP4 = 8'h02, //JMODE = 2

ADD_STEP5 = 16'h0202, REG_STEP5 = 8'h0E, //KM1 = 14 k=KM1+1=15

ADD_STEP6 = 16'h0204, REG_STEP6 = 8'h07, //JCTRL Scramble Enabled use TMSTP+- for sync

ADD_STEP7 = 16'h003B, REG_STEP7 = 8'h01, //enable TMSTP+- input

ADD_STEPG1 = 16'h0029,REG_STEPG1 = 8'h30, //enable sysref receiver,sysref_zoom=1,sysref_sel=0

ADD_STEPG2 = 16'h0029,REG_STEPG2 = 8'h70, //enable sysref processor

ADD_STEPG3 = 16'h02B0,REG_STEPG3 = 8'h01, //enable sysref calibration

ADD_STEPG4 = 16'h82B4, REG_STEPG4 = 8'h00, //read SRC_DONE

ADD_STEP8 = 16'h0062, REG_STEP8 = 8'h05, //CAL_FG = 1 CAL_OS = 1

ADD_STEP9 = 16'h0048, REG_STEP9 = 8'h04, //pre-emphasis

ADD_STEP10 = 16'h0061, REG_STEP10 = 8'h01, //CAL_EN = 1

ADD_STEP11 = 16'h0213, REG_STEP11 = 8'h07, //CAL_EN = 1

ADD_STEP12 = 16'h0200, REG_STEP12 = 8'h01, //JESD_EN = 1 等待ADC响应sync

ADD_STEP13 = 16'h006C, REG_STEP13 = 8'h00, //CAL_SOFT_TRIG = 0

ADD_STEP14 = 16'h006C, REG_STEP14 = 8'h01, //CAL_SOFT_TRIG = 1 检测CALSTAT

ADD_STEP15 = 16'h806A, REG_STEP15 = 8'h00, //rd CAL_STATUS

ADD_STEPG5 = 16'h02C2, REG_STEPG5 = 8'h00, //dismask alarm

ADD_STEPG6 = 16'h02C1, REG_STEPG6 = 8'h1F, //clear alarm

ADD_STEPG7 = 16'h8208, REG_STEPG7 = 8'h00, //read jesd status

ADD_STEPG8 = 16'h82C1, REG_STEPG8 = 8'h00; //read alarm

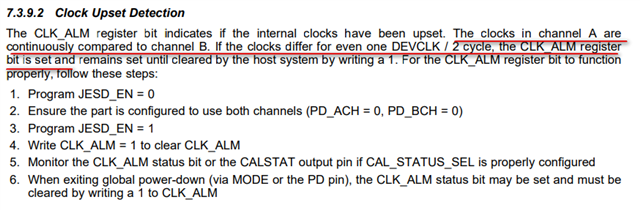

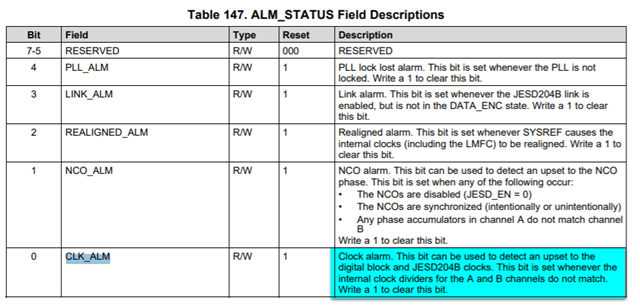

目前的现象就是204B的初始化链路建立不起来,sync信号周期性地拉高拉低,读alarm status寄存器中的clk_alm一直为高,示波器看04828提供的时钟都正常。

请问clk_alm在什么情况下会一直是高,是说明时钟不正常吗?还有请帮忙看一下寄存器的配置是否存在问题?