关于ADS131A04采样保持器,我有一个疑问。

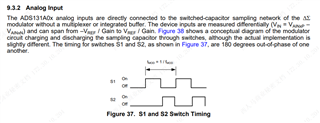

按照ADS131A04手册9.3.2说明(如下图所示),采样保持器的采样频率为fMOD(4.096MHz),也就是采样时间只有T_mod/2(约为0.122uS),这样要是在这个时间内采样电容能达到24bit的精度,就要求输入端的输出阻抗要很小才能满足要求。

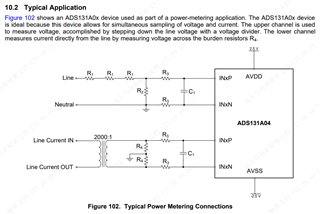

但是按照手册中的典型应用10.2(如下图所示),其中R3=100Ω、C1=2.7nF,作为输入端RC,应该不能在T_mod/2的时间内使采样电容达到24bit(甚至20bit)的精度。如上次您发的培训视频内容:training.ti.com/ti-precision-labs-adcs-introduction-sar-adc-front-end-component-selection

所以我想请问一下,是不是我对于ADS131A04的采样保持过程或者是采样时间理解存在误区。

期待得到您的指导!!!