以前设计过12个AD7175同步采集 方案是公用SCLK、DIN、DOUT 不同GPIO控制不同ADC的CS 是没问题的因为DOUT是三态输出、CS高电平失能情况下为高阻状态 测试12个DOUT并联是可以正常使用的

结构如图(项目已测试,使用是OK的)

现在有个场合需要32路ADC AD选的是ADS1220初步计划:

SCLK、DIN通过74HC573(8路) 4路用于SCLK 4路用于DIN 每8个ADS1220公用一个IO

麻烦的是DRDY、DOUT/DRDY、CS处理

目前问题如下

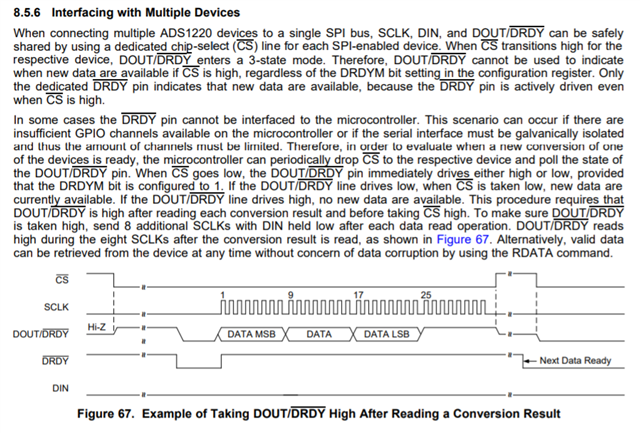

1.还是按照7175那个设计的话32个DOUT接一起不知道有没有问题

2.DRDY要不要省略

3.如果所有ADC公用CS 不同DOUT 是否可行?

4.保证AD时钟同步的情况下 是不是可以用方法3

实在没有什么办法的情况下 打算是用64个IO 32个DOUT 32个CS 采用连续读取模式DRDY省略掉

能节省些IO当然节省一些好 程序写起来也相对简单点