Part Number: ADS1256

对于24bitADC的测试,1.通常对ADC 的时钟都有比较高的要求,对于24 ADC测试中时钟模块的外围电路设计应该如何去设计?

2.对于ADS1256 EVM 板子中电路图J2是个什么模块,有什么作用呢?该模块错采用的芯片型号又是多少呢?

电路图网址如下:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: ADS1256

对于24bitADC的测试,1.通常对ADC 的时钟都有比较高的要求,对于24 ADC测试中时钟模块的外围电路设计应该如何去设计?

2.对于ADS1256 EVM 板子中电路图J2是个什么模块,有什么作用呢?该模块错采用的芯片型号又是多少呢?

电路图网址如下:

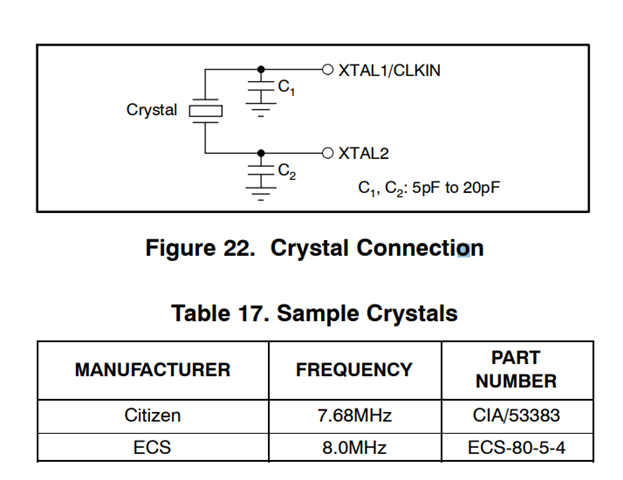

您好,外部晶振的接法可参考数据手册的Figure22,datasheet中给出了两种推荐的型号,另外也可以参考这篇应用手册,也可以使用陶瓷谐振作为时钟发生器,具体您参考下这篇手册:https://www.ti.com.cn/cn/lit/an/sbaa104/sbaa104.pdf

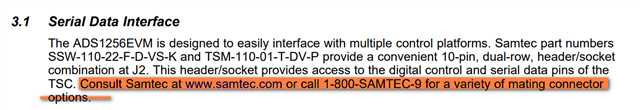

J2是个串口连接器,比如使用一个带这个串口的排线,用来连接demo和电脑的。

J2是个串口连接器,类似下图中的connector。 EVM use's guide给出了J2的厂商Samtec。

这里使用transformer的目的和使用全差分运放的道理是一样的,目的是把单端输入的CLK变成差分信号,可以看到待测芯片接的是差分CLK。

使用差分信号能够更好的抑制共模带来的干扰。