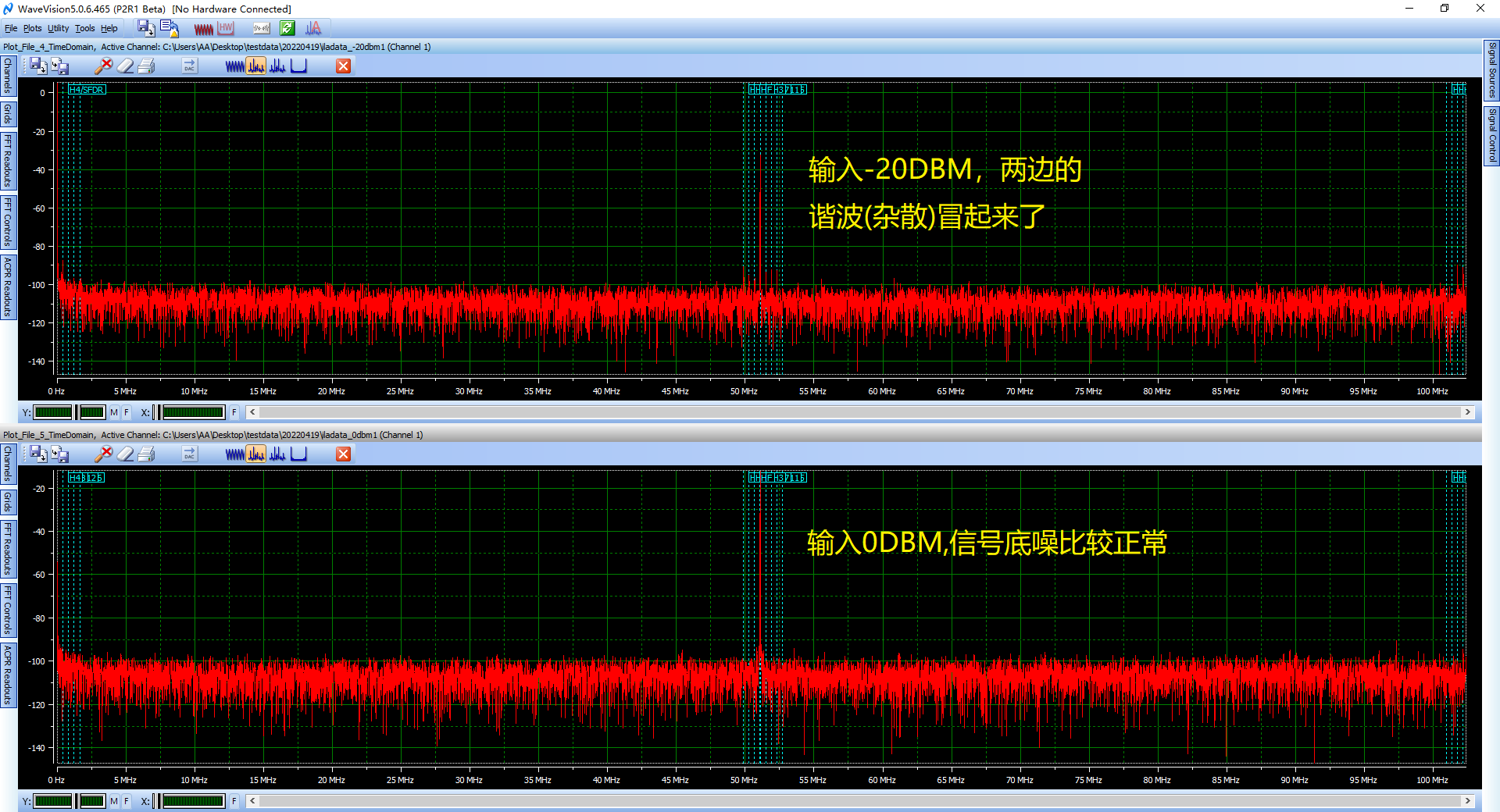

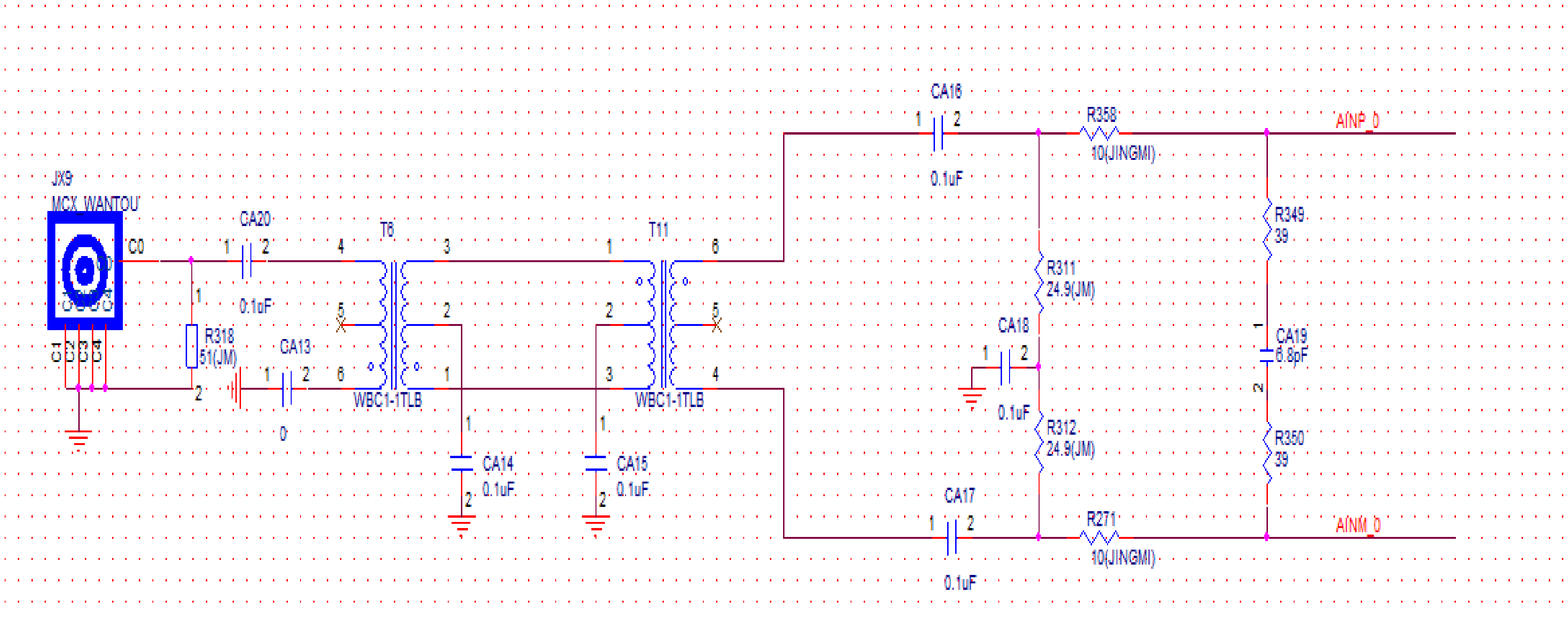

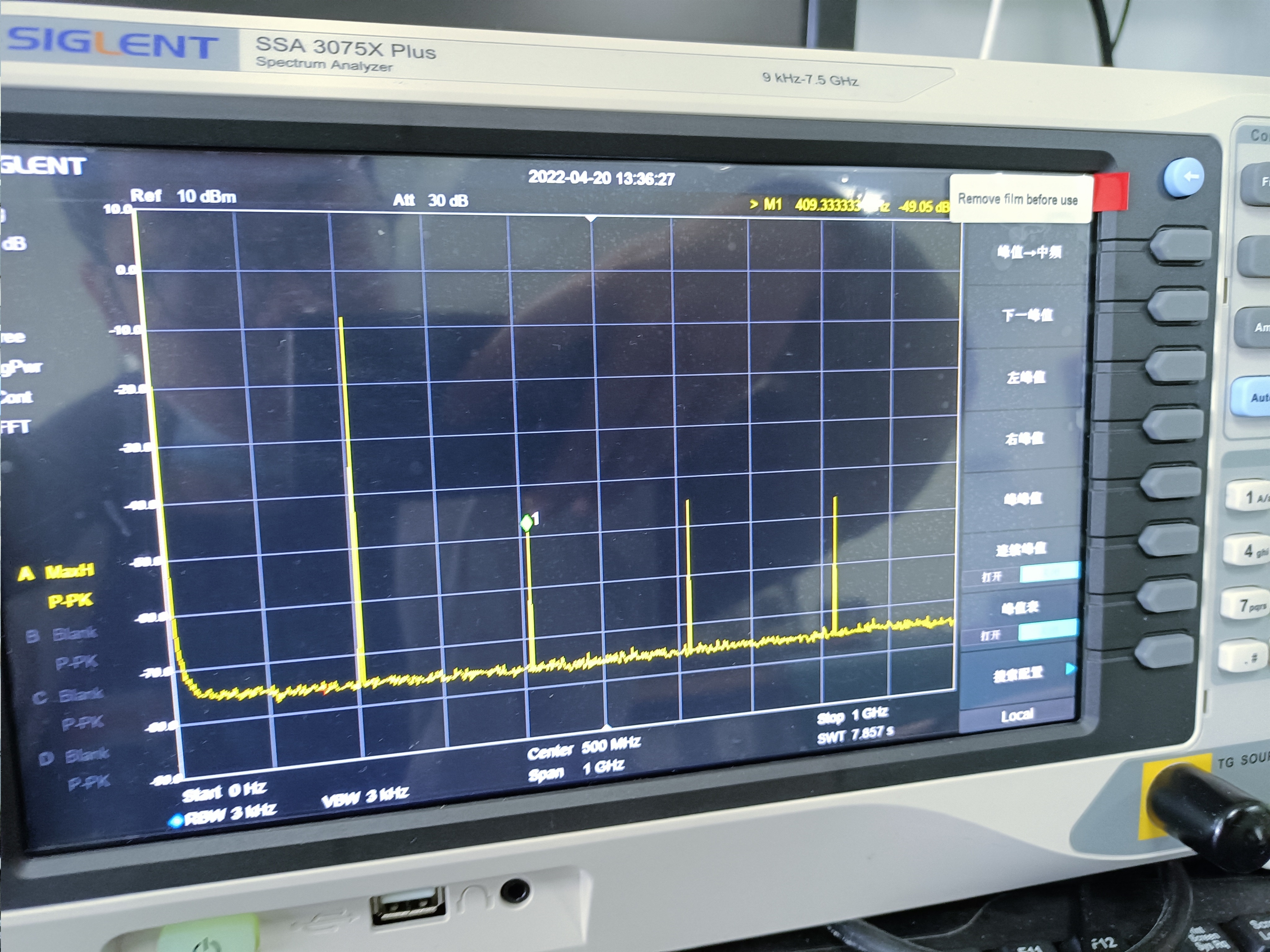

输入外时钟采样率204.8兆,在外界输入信号0DBM时候,中心频率153.7M,信号外部加了带通滤波器,频谱基本正常,杂散很小(wavevision分析均是多次谐波),也基本符合器件特性。但是输入信号到-22~~-40dbM时候,信号的两边的杂散反而变高,并没有跟随信号输入幅度的降低而减弱。具体见下图的黄色文字。在几个不同的板型上均发现该问题,现在主要疑惑是为什么信号输入幅度降低的时候,两边的杂散反而增加。我们怀疑这个是ADC本身采样带来的问题。可以排除信号源和时钟的问题,换了不同的信号源均是这个问题。第二个图是我们的前端电路。