Other Parts Discussed in Thread: THS4552,

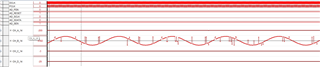

采用ADS6442采集四路正弦波,采样率10MHz。四路频率100KHz幅度1Vpp的单端正弦波通过两片THS4552转为差分DC耦合至ADS6442,THS4552的共模输入来自ADS6442的共模输出,以满足ADS6442输入要求。ADS6442的四路LVDS输出送给Altera的FPGA。但是四路信号不同程度出现乱码,其中C路最好,D路次之,A,B路最差。A,B路的模拟输入来自同一片THS4552,C,D路的模拟输入来自另一片THS4552,两片THS4552的设置完全相同。以下是FPGA端的采集截图:

1.四路无输入信号情况:

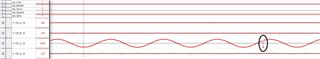

2.C路输入信号情况:

3.A路输入信号情况:

4.B路输入信号情况:

请问这是什么原因造成的?谢谢!