您好:

我们想使用ADC32J25这款ADC,在看芯片规格书的过程中,有个参数需要请教确认一下:

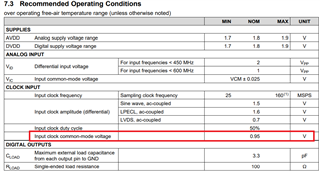

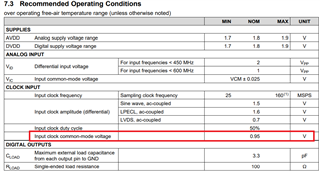

Input clock common-mode voltage 是0.95V,是否意味着我输入的时钟如果是方波,对地做参考时,高电平只能是0.95V。

芯片的供电是1.8V,那么芯片的通信SPI数据电平也是1.8V是吧

感谢回复!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好:

我们想使用ADC32J25这款ADC,在看芯片规格书的过程中,有个参数需要请教确认一下:

Input clock common-mode voltage 是0.95V,是否意味着我输入的时钟如果是方波,对地做参考时,高电平只能是0.95V。

芯片的供电是1.8V,那么芯片的通信SPI数据电平也是1.8V是吧

感谢回复!

您好这里指的是时钟输入的共模电压为0.95V。

举个例子,比如时钟信号的峰值为2Vpp,那么以0.95V为参考,即为-0.05V~1.95V的信号。

SPI是数字信号,所以参考的是DVDD,DVDD电压也是1.8V,所以SPI也是1.8V没问题。

感谢您的回复。

这里再请教一下,ADC的时钟输入是差分输入,那么对于单端信号,输出的电平在-0.05V~1.95V范围内就是没问题的是吧?

还有,这个时钟的频率,是对应于ADC的转换频率还是说我可以自己定义需要的时钟频率呢?

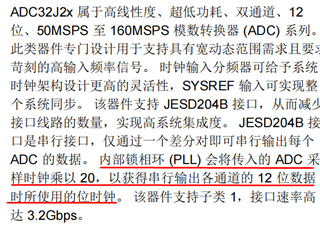

您好,补充以上问题,ADC32J25规格书上如下的描述,所说的采样时钟是否就是我们输入ADC的时钟呢?

ADC的时钟输入是差分输入,那么对于单端信号,输出的电平在-0.05V~1.95V范围内就是没问题的是吧?

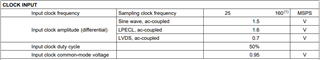

您的意思是clock使用单端输入是吗?电气参数表格里给出,比如LVPECL输入,幅值为1.6V,这个是差分输入的情况下。

那么单端输入的话,单端信号的幅值为0.8V,因此0.95V为共模电压的话,单端输入的信号应为0.55V~1.35V。

补充以上问题,ADC32J25规格书上如下的描述,所说的采样时钟是否就是我们输入ADC的时钟呢?

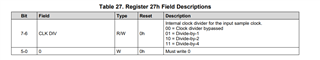

输入clock前端有个分频器,经过分频器的时钟即为采样时钟。

分频是通过寄存器27h bit[7:6]设置的。比如CLKIN 时钟为160Mhz,默认divider为1的话,那么采样时钟就是160Mbps。

可以看到,采样时钟范围为25Mbps~160Mbps,如果采样时钟为160Mbps,divider 配置为4的话,那么输入时钟需要640Mhz的频率。