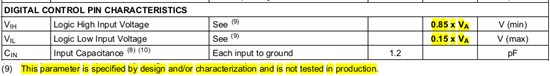

(1)ADC08D500数据手册中给出了控制引脚的VIH和VIL的下限和上限,分别为0.85*VA、0.15*VA,VA一般取1.9V,则VIH和VIL的限制分别为1.615V和0.285V。

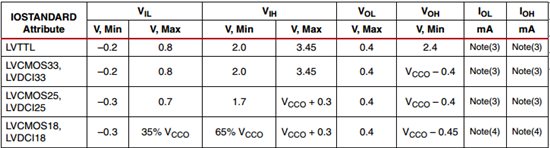

但一般我们用的微机芯片输出的1.8V LVCMOS电平都不在这个范围内,我们看到的这款器件的评估板原理图(NI 公司的BIG GIG REFERENCE BOARD REV. 2.0A)中是将这些控制信号直接与xilinx的FPGA XC4VLX15 的BANK IO直接相连,但从FPGA的参考手册中发现,1.8V LVCMOS电平并不能与之兼容,见下图。网上找到的一些电平转换芯片输出的1.8V电平也基本上是这个范围,这样一来,岂不是难有器件能够满足这款ADC的控制引脚电平要求了?另外上图中的(9)中说这个参数并未在产品中经过测试,我们不明白这意味着什么?

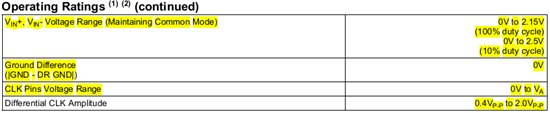

(2)ADC08D500中提到两个地(应该是数字地和模拟地)之间的压差最好为0V,不知这是否意味着需要把两个地直接相连?