Other Parts Discussed in Thread: SN65HVS880

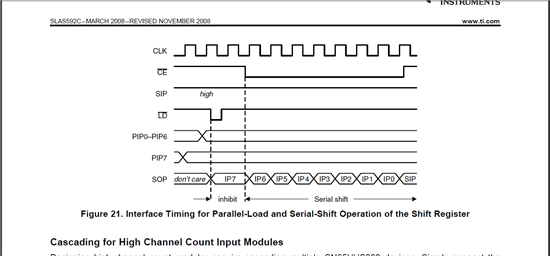

1)上面SN65HVS880 时序图,有点不太明白,为什么SOP的第一位IP7在使能信号CE变为低电平时就被传送出去了,而且下面写着inhibit,是不是说IP7是被抑制

掉了,因为我在用一个SN65HVS880调试时发现当我没给并行口数据时,串行口接收到的数据总为0000 0001。

2)给IP7高电平时,数据时加载不到串行口的,其它的6个并行口能加载到,0000 0001中的最低位中的1是不是因为没串接下一个SN65HVS880引起的呢?是不是

一个完整的8位数据时IP6 IP5 IP4 IP3 IP2 IP1 IP0 SIP,而不是IP7 IP6 IP5 IP4 IP3 IP2 IP1 IP0?

3)还有一个问题是SN65HVS880是不是在CLK的上升沿发送数据出去的?

谢谢。