adc08d1020的所有控制线(1.9V电平)接入 xilinx V5芯片 电平为3.3V的IO BANK,现板子已做好,没有办法换FPGA的IO电平。

控制线有三种:

1)可以直接接高电平(1.9v)或接地,这种可以通过上下拉电阻控制 。

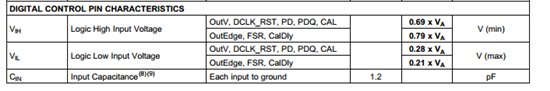

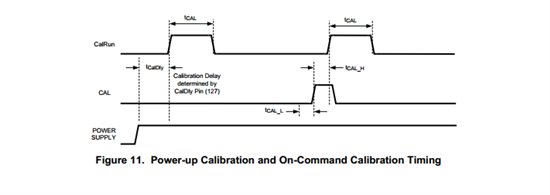

2)FPGA输出脉冲给AD,即3.3V驱动1.9V 如Pin 30 CAL: Calibration Cycle Initiate.

3)AD输出脉冲给FPGA,即1.9V 驱动3.3V ,如Pin 126 CalRun:Calibration Running indication.

请问:

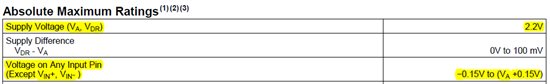

- 对于2)由于AD的输入端有钳位,VA =1.9V,如下图,是否3.3V驱动1.9V 没有问题?如果有问题该如何解决?

2. 对于3)AD输出高电平是不是驱动不了FPGA的逻辑1?(FPGA 用的是XILINX V5 )可有解决的办法?