Other Parts Discussed in Thread: ADC3664

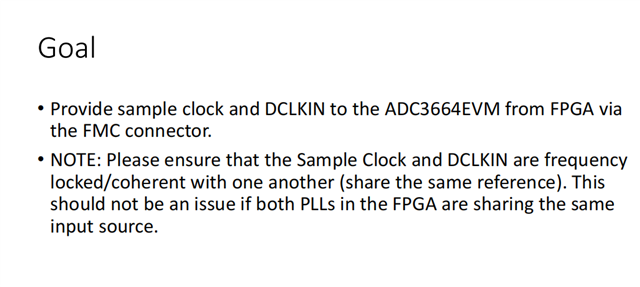

根据ADC3664EVM_FMC_Clocking.pdf文档进行修改后,即实现如下图所示功能

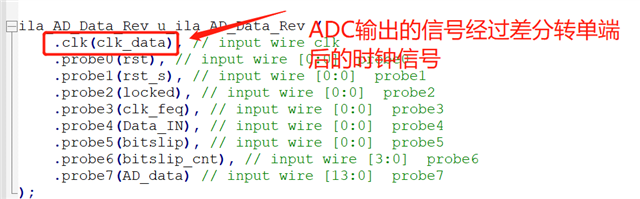

问题: (tip:FPGA的程序中仅有图一所示的这一个ILA核)

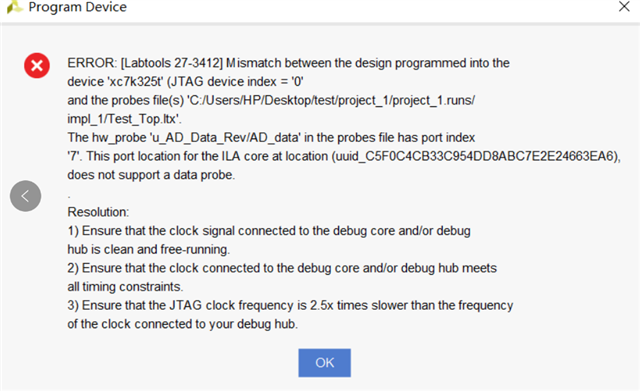

我在FPGA有一个ILA核,这个ILA核的时钟信号是clk_data,如下图一所示,这个时钟信号是由ADC3664的DCLKP、DCLKM引脚经过差分转单端而生成的。请问为什么在生成bitstream后下载给FPGA之后会出现下图二所示的错误。

我个人认为是因为这个ILA核的时钟clk_data是由ADC的DCLKP、DCLKN引脚的差分信号所提供的,而这对差分信号产生的前提是ADC的DCLKINM、DCLKINP有输入信号(实际上DCLKINM、DCLKINP是由FPGA提供给ADC的,我在程序中也有相关代码以实现FPGA给ADC提供DCLKINM、DCLKINP信号)。 这其实就有一个冲突:即FPGA提供DCLKINM、DCLKINP信号给ADC3664后ADC3664才返回DCLKP、DCLKN信号来作为ILA的时钟信号clk_data。而FPGA在进行调试前是需要有clk_data信号的。这就使得一方面bitstream没办法下载进去FPGA从而给ADC提供DCLKINM、DCLKINP信号,另一方面ADC又会因为没有DCLKINM、DCLKINP信号而进一步没有DCLKP、DCLKM信号,这样FPGA也没有调试界面。

请问如何解决这种冲突呢?