Other Parts Discussed in Thread: , CDCE6214

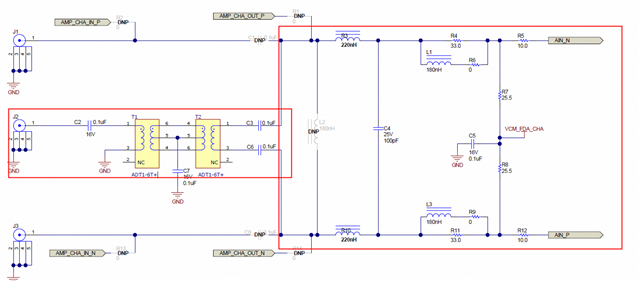

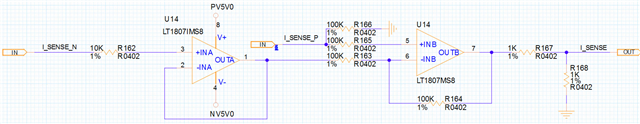

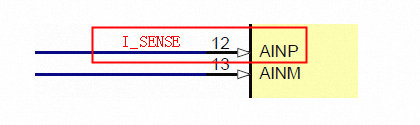

hi , I plan to use ADC3664 for high-speed data acquisition, mainly collecting the voltage difference between the two ends of the resistance and then collecting the current. Because the sampling resistor and the ADC3664 chip are not on a PCB, in order to reduce the error, I plan to output the single-ended signal to the ADC after the voltage at both ends of the sampling resistor is processed by the subtractor.The specific circuit picture is as follows, please help to see whether this design is OK?

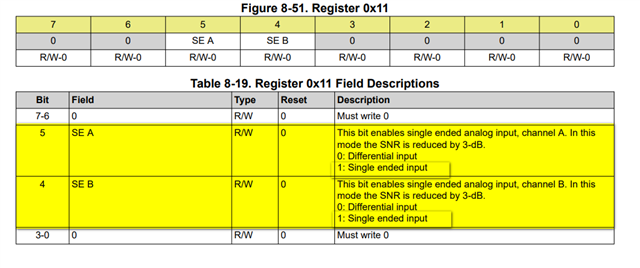

In addition, the differential input of ADC3664 is used as a single-ended input after the above design. Is it ok to use it in this way?I see nothing in the spec says it can be used as a single end, nor does it say it can't. If yes, I use the AIN_P pin, then how to operate the AIN_M pin, floaing or ground?

Looking forward to your reply, thank you!