我也碰到同样的问题,请教一下:

1. 测试DC test signal, 发现数值大小约0.127VREF,与datasheet上描述的2/15VREF相差较大,请问这个是什么原因?

2. 我们很清楚,严格的校准是需要校准整个信号链;但我们想尽可能减小ADC本身的long-term gain drift,延长设备的校准周期,是否可以通过检测DC test signal来换算增益校准系数来实现?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

1. 我们使用的是线性电源,内部参考源1.2V电压,电源确定是稳定、干净无干扰的,纹波很小,LDO 3.3V。这个得到0.127VREF而不是2/15VREF不止是我们遇到过,看论坛上有类似帖子(e2echina.ti.com/.../ads131m04-39),原因不明;

2. 我们的设备属于高精密测量设备,运行要求比较高,要求整体信号链校准间隔时间180天,连续24小时不断电运行,但每天有空闲时间做电路内部自校准工作,因此对ADC器件的gain drift要求较高,我们希望用内部DC TEST SIGNAL 自动校准增益漂移,但不确定这个DC TEST SIGNAL的可靠性,可以做为增益误差或漂移校正的依据么?

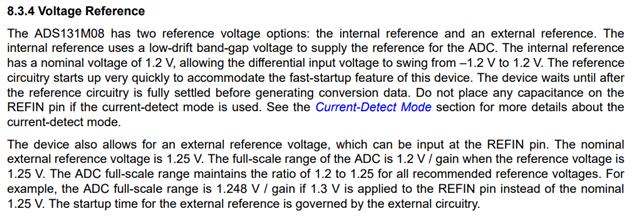

2. 我们也留意到reference drift与Gain drift差不多,最大在20ppm/°C, 偏大一点,性能不是很好;因此我们是打算用外部性能比较好的Reference;

3. 因ADC内部的DC test signal是由ADC internal reference分压而来,这样是不是配置为内部reference使能,可以用这个DC test signal定期校准gain drift?

4. 在正常测量模式下,配置为外部性能较好的external reference使能。

5. 我们的应用中,一般只用到增益1.

请教几个问题:

1. 这种方式校准gain drift是否可行?

2. ADC的reference引脚同时连接external reference, ADC内部配置是否支持如上功能操作,外置的external reference芯片与ADC ref引脚之间是否需要放一切换开关?(ADC引脚同时连接到外部基准芯片会不会影响内部reference使能)

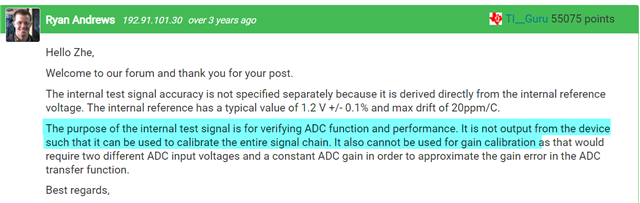

感谢您提供的链接,看了链接中Ryan的回复,指出内部测试信号用于验证ADC的功能和性能,它不能用于校准整个信号链,也不能用于增益校准。

另外看下面帖子Dale回复,如果使用内部基准电压1.2V,基准电压会有一个衰减,即衰减1.2/1.25倍,实际基准电压应为1.2/1.25*1.2=1.152V。这样计算 DC test signal电压为153.6mV。另外,我猜测2/15这个比例应该也有误差,如下帖子Dale回复我们没有DC test signal的准确性的数据

ADS131M06: Accuracy of internal test signals

2. ADC的reference引脚同时连接external reference, ADC内部配置是否支持如上功能操作,外置的external reference芯片与ADC ref引脚之间是否需要放一切换开关?(ADC引脚同时连接到外部基准芯片会不会影响内部reference使能

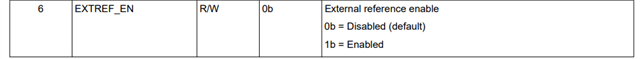

不用,可以使用如下寄存器位配置: