采样时钟用AD9516芯片提供LVDS类型时钟,整个AD采集卡通过FMC接口与FPGA相连。

拿到的demo程序是250M采样的,我现在需要一个50M采样的配置。已经更改了AD9516的输出时钟配置,输出时钟的频率是50MHz。

也改了ads62p49的“enable low speed mode”的寄存器,但是各种测试模式、正弦波出现的波形一直不对。

想问下还需更改哪些ads62p49的配置。除了“enable low speed mode”的寄存器,还需要更改其他的设置?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

采样时钟用AD9516芯片提供LVDS类型时钟,整个AD采集卡通过FMC接口与FPGA相连。

拿到的demo程序是250M采样的,我现在需要一个50M采样的配置。已经更改了AD9516的输出时钟配置,输出时钟的频率是50MHz。

也改了ads62p49的“enable low speed mode”的寄存器,但是各种测试模式、正弦波出现的波形一直不对。

想问下还需更改哪些ads62p49的配置。除了“enable low speed mode”的寄存器,还需要更改其他的设置?

您好,

应该不需要配置其他的了

检查下时钟规格是否符合要求:

在250M采样率下可以正常工作吗?

但是各种测试模式、正弦波出现的波形一直不对。

您测试了哪些测试模式,具体输出是什么样子的?

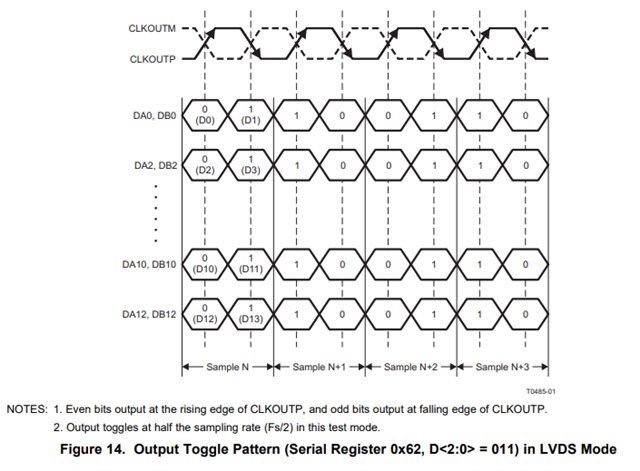

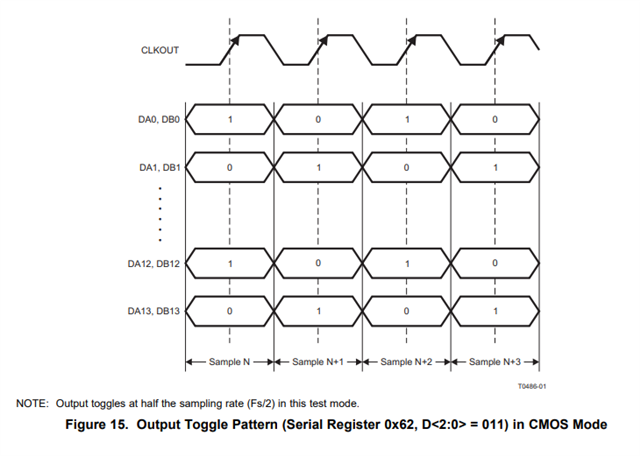

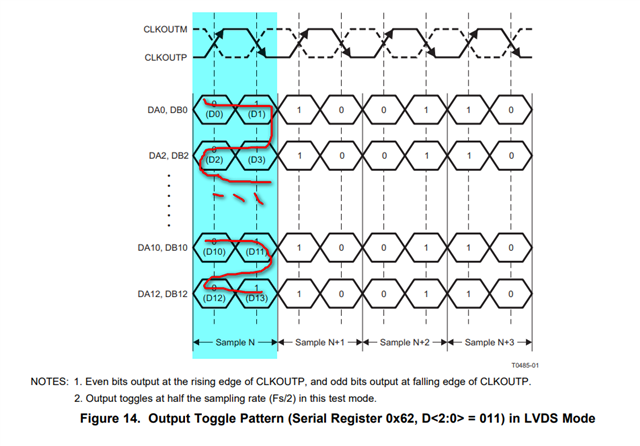

您使用的什么输出模式LVDS还是CMOS?您可以附上像datasheet Figure 14或 figure15这样详细的波形图吗?我想看下时序是否存在问题

使用的是LVDS输出

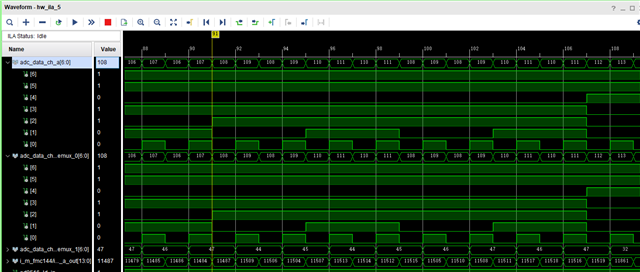

adc_data_ch_a是adc芯片给到FPGA转化后单端数据(测试模式04,digital,50M)

adc_data_ch_a_demux_0 , adc_data_ch_a_demux_1分别对其上升沿采样和下降沿采样

这一张是上升沿采样结果,

adc_data_ch_a_demux_0是对其上升沿采样的结果(滞后于adc_data_ch_a一个时钟周期)

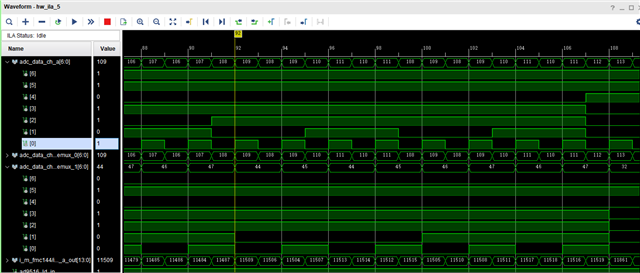

这一张是下降沿的采样结果

adc_data_ch_a_demux_1是对其下降沿采样的结果(滞后于adc_data_ch_a一个时钟周期)

我感觉您是理解错了LVDS的输出格式,它是在输出时钟的上升沿和下降沿都会有输出,在一个时钟周期内输出14bit数据,然后采样sample 数据位 D0至D13 按照如下顺序在管脚上输出:

LVDS输出是在一个CLKOUT时钟周期内输出一个采样数据,这个采样数据的D0, D2, D4...等偶数位在CLKOUTP的上升沿输出,这个采样数据的D1, D3, D5...等奇数位在CLKOUTP的下升沿输出,必须使用CLKOUTP的上升和下降边缘来捕获这个采样数据的所有数据位。

第一行是数据,第二行是上升沿采样,第三行是下降沿采样(延迟一时钟周期)

看您波形图一个采样数据并不是在一个CLKOUT时钟周期内采用完成的,不知道您这里为什么要“延迟一时钟周期”,延迟一个时钟周期,那就是下一个采样数据了。

是的,我已经改正了,在同一个时钟的上升沿和下降沿输出数据,现在结果是对的,可以正常使用。

很高兴有了进展;

之前的250M采样demo,他们将数据延迟了一个周期,结果是对的,不知道他们是怎么配置的

不知道您说的“将数据延迟了一个周期”具体是什么情况,如果是上升沿和下降沿都延迟,那么就是少采一个样本;如果是采用数据的偶数位在CLKOUTP的上升沿采,奇数位在CLKOUTN的上升沿采,也是可以的。关键是在一个CLKOUT周期内完成采样。如果是偶数位在一个CLKOUT周期内采,而奇数位在下一个CLKOUT周期内采,那么不对了。