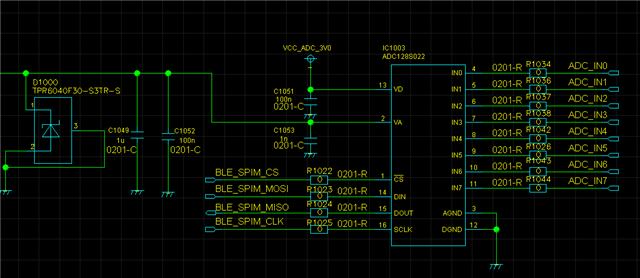

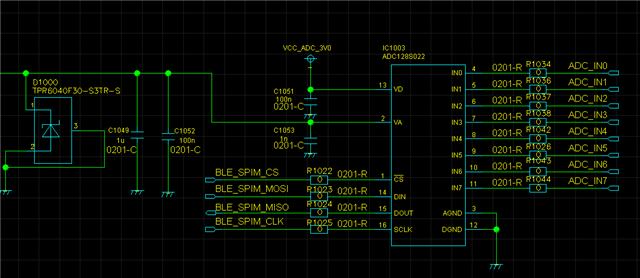

现象描述:断掉VA 和VD的供电,VA依旧有2.2V左右的电压。(其中VD=3V,VA=3V,SPI接口电压=3.04V))

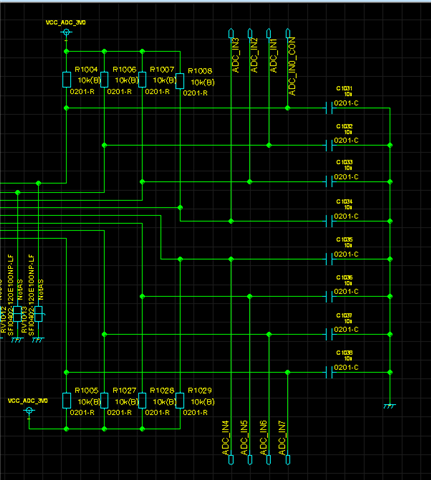

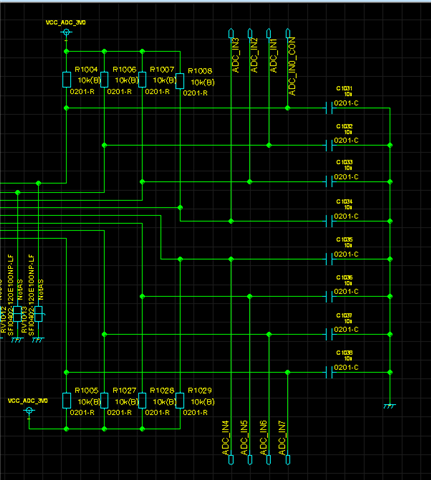

经查发现是从SPI引脚和IN0~IN7个ADC引脚漏过来的电。(SPI正常为3.0V高电平,IN0~IN7为3.0V高电平)

问题:

1、这样漏电现象是否正常?

2、漏电的原因是什么?

3、应该如何解决这个漏电问题?(IN0~IN7要一直保持高电平)

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

现象描述:断掉VA 和VD的供电,VA依旧有2.2V左右的电压。(其中VD=3V,VA=3V,SPI接口电压=3.04V))

经查发现是从SPI引脚和IN0~IN7个ADC引脚漏过来的电。(SPI正常为3.0V高电平,IN0~IN7为3.0V高电平)

问题:

1、这样漏电现象是否正常?

2、漏电的原因是什么?

3、应该如何解决这个漏电问题?(IN0~IN7要一直保持高电平)

您好,漏电肯定是不正常的,就这一块板子吗?其他的板子有没有试?

漏电的原因比如这块PCB板上是否有其他残留物导致的漏电,或者这块板子可能已经损坏导致的,另外,这片ADC可能也异常了导致漏电都有可能 ,所以建议您测试下其他板子。

之前描述错了 漏电是从SPI接口 漏到VA的

怎么判断是SPI接口漏电到VA的?是否有VA还没上电,SPI接口给了信号的操作?或者说SPI和主机连接,一直在通电状态,而VA后上电的情况?

我担心这样操作的话,内部电路从SPI到VA有电流存在,相当于给VA供电,一旦超过可允许最大电流,会直接将ADC损坏。

您好,您提到了休眠,我看了下这块ADC没有low power 管脚去控制其进入休眠状态,这样的话可保证芯片内部其他电路也处于休眠状态。

如果是通过外部断电使其进入low power 状态,那么SPI 数字电路部分仍是工作的,这样就很难保证芯片稳定性。

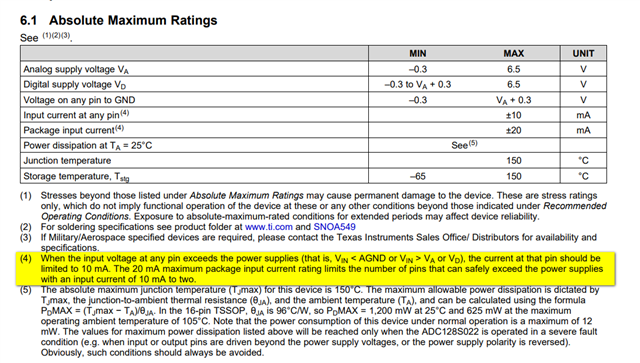

在这颗芯片“电气参数最大值”表格下满有备注,您看下,任何输入引脚大于VA或VD,或者小于GND的话,有个10mA的限流,就像我上面提到的相当于给VA或VD供电,所以会看到即使断电,VA或VD处仍有电压存在。