工程师您好!

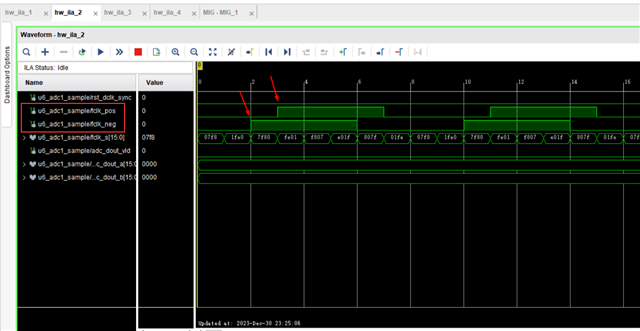

我们使用FPGA抓取FCLK时发现其P和N不同步:

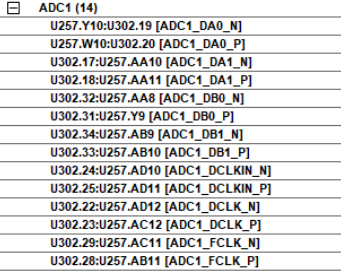

但是我们这些差分线都是做了等长的,如下:

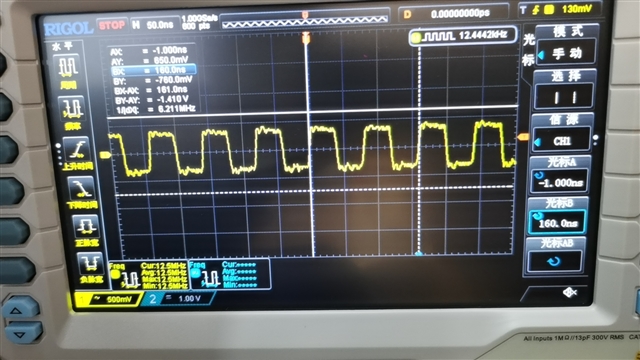

捕获的FCLK一端如下:

请问会是什么问题造成的呢?

有疑惑是这个FCLK的摆幅是否正常?其与FPGA是直连,还是有要求P和N之间要跨接100欧电阻呢?

感谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

PN相位差多少?最好使用差分碳棒在输出端测下差分信号。

测试得到的FCLK的幅值是650mV是吗?共模电压是1V是吗?这样的话幅值应该是正常的。

FCLK是差分LVDS时钟输出,datasheet中给出了LVDS的幅值范围500mV~850mV,典型值700mV。共模电压为1.0V。

您提到了和FPGA直连,如果FPGA的LVDS输入端内部没有端接100ohm的话,是需要外部在靠近FPGA的输入端跨接100ohm电阻的。

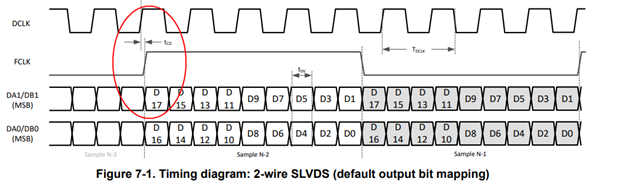

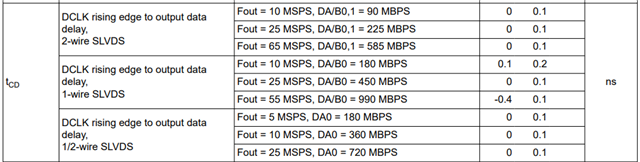

FCLK为frame clock,DCLK为LVDS bit clock。DCLK和FCLK的输出延迟即为时序图中的tCD,DCLK和output data之间的延迟,也是DCLK和FCLK之间的延迟,可以看到不论是1 wire LVDS 还是2-wire LVDS模式,这个延迟典型值差不多在0.1ns左右。

您目前测试得到的延迟为多少?如果在这个范围内,我想FPGA采集有误和这个延迟无关了。