请问,传统四线SPI的情况下,在一区传输模式中,利用MCU(SPI给的60MHZ最大;MCU主频480MHZ),它的采样速率理论上是多少,在正常设计中是否还会降低?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好

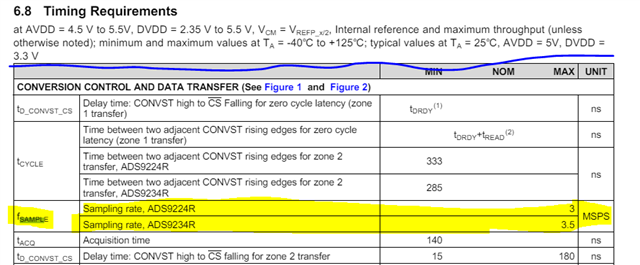

根据官方datasheet采样速率如下,这是官方在如图条件测试出来的数据请您参考。

关于设计的部分问题请您参考以下建议:

ADS9234R 是一款高性能的模数转换器(ADC),其数据接口通常支持多种通信协议,包括 SPI(Serial Peripheral Interface)。在考虑 SPI 通信下的采样速率时,我们需要考虑几个关键因素:

SPI 时钟频率:SPI 的最大时钟频率限制于 ADC 和 MCU 两者中较低的那一个。在这里,您提到 SPI 给了 60MHz 的最大频率,而 MCU 主频为 480MHz。但 SPI 通信并不直接使用 MCU 的主频,而是使用分频或专门的 SPI 时钟。因此,60MHz 是 SPI 通信的限制频率。

数据传输格式:SPI 传输数据通常是按位进行的,而且可能有额外的开销位(如开始位、结束位、帧同步位等)。ADS9234R 可能支持不同的数据格式和位数,这会影响每次传输的数据量。

转换时间:ADC 的采样速率还受限于其自身的转换时间。即使 SPI 能够以非常高的速率传输数据,ADC 也需要一定的时间来完成一次转换。

数据准备和读取时间:在 SPI 通信中,MCU 需要时间来准备数据以发送,或者从 ADC 读取数据。这包括处理中断、读取/写入数据寄存器等操作。

系统负载和延迟:如果 MCU 还需要处理其他任务,那么 ADC 的采样速率可能会受到系统负载和延迟的影响。

硬件和软件的实现:硬件连接的质量、软件的优化程度等都会影响 SPI 通信的效率和 ADC 的采样速率。

理论上的采样速率:

如果 SPI 以 60MHz 运行,并且每次传输都是连续的(没有额外的开销位),那么理论上每秒可以传输的位数是 60MHz × 每位所需的时间(这取决于 SPI 的工作模式,如 CPOL 和 CPHA 的设置)。但是,这并不意味着 ADC 的采样速率就是这么多,因为还需要考虑 ADC 的转换时间和 MCU 的数据处理时间。

正常设计中的降低:

在实际设计中,采样速率通常会低于理论值,因为需要考虑到上述的各种因素。为了获得最佳的采样速率,通常需要进行硬件和软件的优化,以及仔细的系统设计。