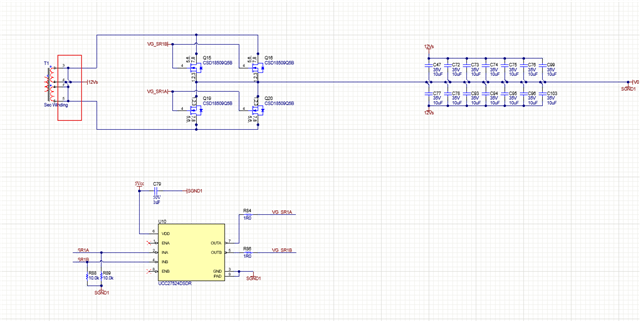

I found the SR Board design files in the zip file of the CAD/CAE symbols. I have a question, why is the transformer on the secondary side short-circuited, so that the transformer has no function.

I found the SR Board design files in the zip file of the CAD/CAE symbols. I have a question, why is the transformer on the secondary side short-circuited, so that the transformer has no function.

在使用AUDIO-AM275-EVM芯片,需要获取该芯片上关于802.1 Qav配置方法,麻烦给与支撑。

您好,

我适配了X3C摄像头,但是使用python脚本取流的时候报错“[ERROR] Error pulling tensor from GST Pipeline”。另外,若单独使用GStreamer命令取流是成功的,这是为什么呢?谢谢

root@j721e-evm:/opt/edgeai-gst-apps# GST_DEBUG=2 ./apps_python/app_edgeai.py configs/ox03c10_cam_example…

TI大部分开关升压的器件都有RT/SSYNC引脚,但对使用外同步频率的方法介绍都是一带而过,如:LM5022就罗列了几个条件:

6、无论是自由振荡器的运行还是用外部同步…

当前手里有一块am62a 的开发版,系统sdk 9.2, 已经转好板端模型,能正常运行模型得到正确结果。期间碰到一个问题:模型推理过程中,如果程序崩溃或者在检测过程中强行C掉程序,简单讲,没有正确执行最后的资源释放代码,就会导致,下一次无法正确运行模型,只能重启板子。报错如下:

libtidl_onnxrt_EP loaded 0xed32db0

Final number of subgraphs created are : 1, - Offloaded Nodes - 132, Total…

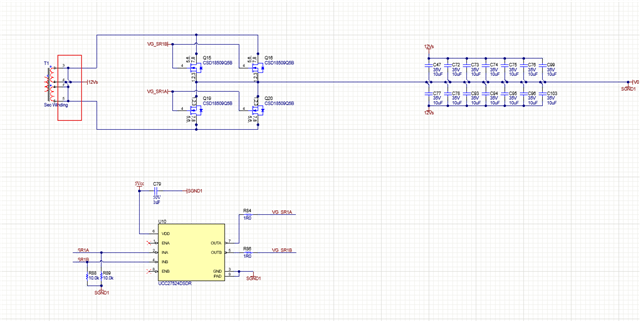

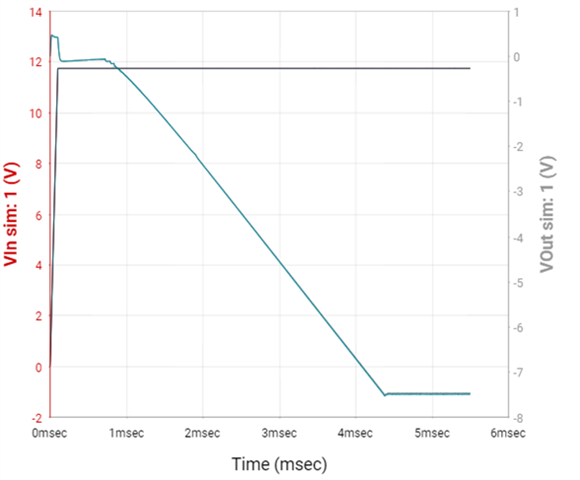

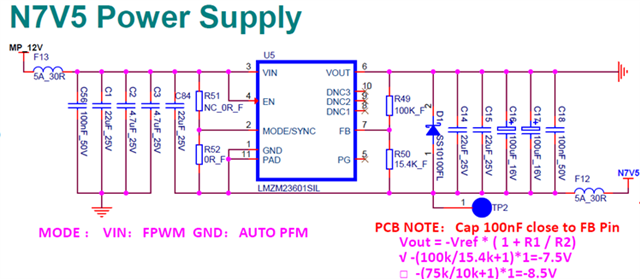

通道一为12V_IN,通道二为N7V5输出,通道三可忽略

条件:Vin=12V,Vout= -7.5V

电流Iout方面目前可忽略,输出后面未带载连接

图一为器件仿真图,图二为实际运用场景下实测波形,图三为实际设计原理图,芯片用于输出负压,可以看见,在输出时,波形会先抬高再开始上电至设计值,此抬高是0V以上的,顶端值最大观测到400mV左右…

transact.ti.com/.../AFE7799

返回: