Other Parts Discussed in Thread: SN74LVT245B

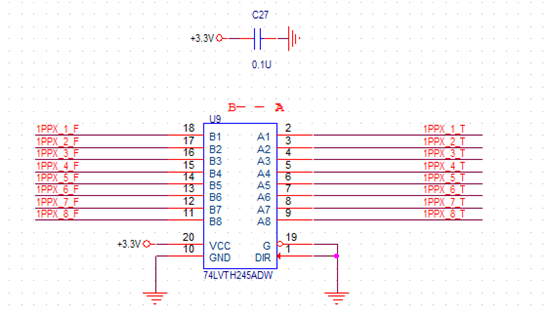

电路如下所示(其中一路):B端与FPGA连接,A端各路连接至光耦。(经过buffer信号的频率均为1Hz)

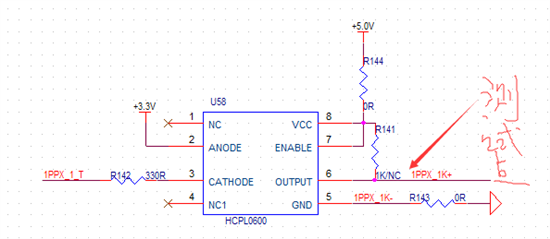

图2

测试一、

测试图2中6脚的信号(示波器不限制带宽、阻抗选择50欧姆)如下图所示:信号幅度依然没有3.3V-0.2V=3.1V,且信号上升沿处有过冲和回沟。这个回沟低于2.0V的判决电平,导致接收端不能识别。

测试二、

测试图2中6脚的信号(示波器制带宽20M、阻抗选择50欧姆)如下图所示:信号上升沿没有过冲和回沟。信号幅度依然没有3.3V-0.2V=3.1V

测试三、

按照datasheet手册的测试电路连接,去掉上面电路中的光耦,示波器贷款不限制,阻抗50Ω,如下图所示:

图中红圈部分为测试点:从下面的测试波形看,有很大的提高。至少回沟高于2.0V。

疑问点:

1、首先从限制带宽就可以把回沟和过冲去掉,说明存在干扰(震荡?信号反射?),如果是的话,电路上怎么解决?如果不是,真正的原因是什么?

2、为什么LVT245这个buffer当示波器的阻抗设置为50Ω的时候,输出信号幅度只有2.5V左右;当示波器的阻抗设置为1MΩ的时候,输出信号幅度就可以达到VCC-0.2V左右;而实际我们信号传输的阻抗是50Ω,这怎么解释呢?

3、以上电路设计是否有什么缺陷?

请大神不吝赐教,小弟不胜感激!