Hi Ti工程师:

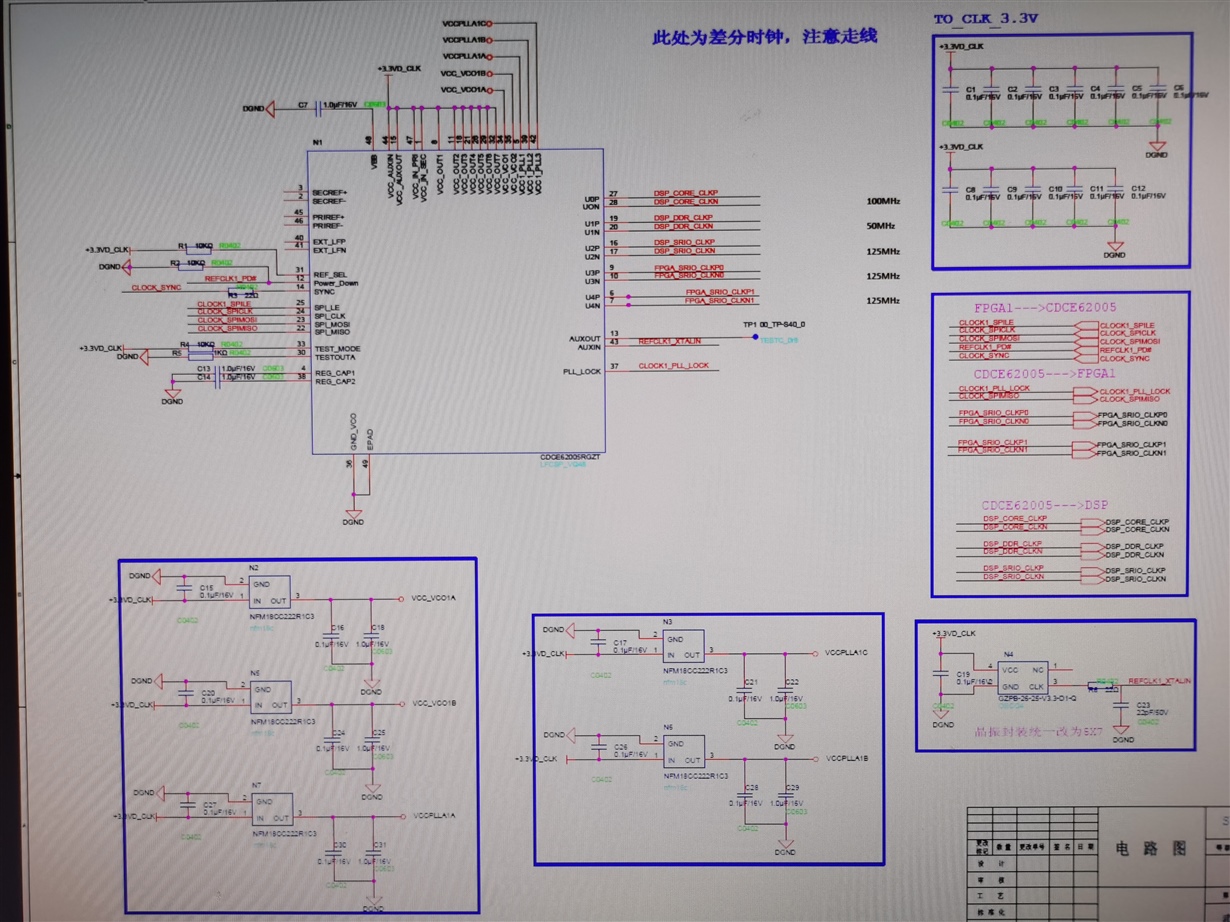

现有使用TI的一款CDCE62005的时钟芯片,电路设计图见附件,在进行电路故障测试性试验过程中,发现如下与预期故障检测不符的情况的:

1、仅断开N2位号穿心电容,模拟34引脚VCC_VCO1断开,预期故障:差分时钟均无法正确输出,实际测试情况:差分时钟正常输出;与预期不符,请问是否正常?为什么?

2、仅断开N5位号穿心电容,模拟35引脚VCC_VCO2断开,预期故障:差分时钟均无法正确输出,实际测试情况:差分时钟正常输出;与预期不符,请问是否正常?为什么?

3、仅断开25MHz晶振的输出得R6电阻,模拟43引脚的AUXIN悬空,预期故障:差分时钟均无法正确输出,实际测试情况相符。但是仅将25MHz晶振的输出滤波电容C23短路,模拟43引脚的AUXIN接地,预期故障:差分时钟均无法正确输出,实际测试依旧正常输出,实际测试情况与预期不符。请问为什么AUXIN悬空和接地的输出情况不一样,接地无输入依然可以正常输出差分时钟?

急盼尽快回复,谢谢 !

!