Other Parts Discussed in Thread: SN65DSI85, , SN65DSI84

使用SN65DSI85将single MIPI信号转换成dual LVDS信号。

通过I2C写寄存器,读寄存器确认写命令都成功了。

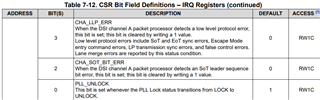

但是读0XE5寄存器,返回值是0x09. 请问0XE5寄存器的错误码代表什么意思呢?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

使用SN65DSI85将single MIPI信号转换成dual LVDS信号。

通过I2C写寄存器,读寄存器确认写命令都成功了。

但是读0XE5寄存器,返回值是0x09. 请问0XE5寄存器的错误码代表什么意思呢?

E5读取值为0x09,说明bit3和bit1为1,bit1=1 代表的PLL未锁存,bit3=1代表的是主机检测到低级协议错误。包括包括 SOT 和 EOT 同步错误、退出模式输入命令错误、LP 传输同步错误和错误控制错误。

另外,读取E5报错,是否有按照datasheet中的初始化的步骤进行初始化,其中第10步配置E5和E6 为FF对这两个寄存器清零?

时序是按照datasheet的初始化步骤初始化的,以下代码是在 MIPI LP11写入命令和HS state检查0xE5寄存器。

因为是single mipi,所以没有检查0xE6寄存器。

//call in LP11 state

//init seq 5,6,7

static int sn65dsi_reg_init(void)

{

int ret = 0;

pr_err("%s\n",__func__);

ret |= sn65dsi_write_reg(0x09, 0x00);

ret |= sn65dsi_write_reg(0x0A, 0x05);

ret |= sn65dsi_write_reg(0x0B, 0x28);

ret |= sn65dsi_write_reg(0x0D, 0x00);

ret |= sn65dsi_write_reg(0x10, 0x26);

ret |= sn65dsi_write_reg(0x11, 0x00);

ret |= sn65dsi_write_reg(0x12, 0x59);

ret |= sn65dsi_write_reg(0x13, 0x00);

ret |= sn65dsi_write_reg(0x18, 0x78);

ret |= sn65dsi_write_reg(0x19, 0x00);

ret |= sn65dsi_write_reg(0x1A, 0x03);

ret |= sn65dsi_write_reg(0x1B, 0x00);

ret |= sn65dsi_write_reg(0x20, 0x80);

ret |= sn65dsi_write_reg(0x21, 0x07);

ret |= sn65dsi_write_reg(0x22, 0x00);

ret |= sn65dsi_write_reg(0x23, 0x00);

ret |= sn65dsi_write_reg(0x24, 0x38);

ret |= sn65dsi_write_reg(0x25, 0x04);

ret |= sn65dsi_write_reg(0x26, 0x00);

ret |= sn65dsi_write_reg(0x27, 0x00);

ret |= sn65dsi_write_reg(0x28, 0x20);

ret |= sn65dsi_write_reg(0x29, 0x00);

ret |= sn65dsi_write_reg(0x2A, 0x00);

ret |= sn65dsi_write_reg(0x2B, 0x00);

ret |= sn65dsi_write_reg(0x2C, 0x2c);

ret |= sn65dsi_write_reg(0x2D, 0x00);

ret |= sn65dsi_write_reg(0x2E, 0x00);

ret |= sn65dsi_write_reg(0x2F, 0x00);

ret |= sn65dsi_write_reg(0x30, 0x05);

ret |= sn65dsi_write_reg(0x31, 0x00);

ret |= sn65dsi_write_reg(0x32, 0x00);

ret |= sn65dsi_write_reg(0x33, 0x00);

ret |= sn65dsi_write_reg(0x34, 0x94);

ret |= sn65dsi_write_reg(0x35, 0x00);

ret |= sn65dsi_write_reg(0x36, 0x24);

ret |= sn65dsi_write_reg(0x37, 0x00);

ret |= sn65dsi_write_reg(0x38, 0x58);

ret |= sn65dsi_write_reg(0x39, 0x00);

ret |= sn65dsi_write_reg(0x3A, 0x04);

ret |= sn65dsi_write_reg(0x3B, 0x00);

ret |= sn65dsi_write_reg(0x3C, 0x10);

ret |= sn65dsi_write_reg(0x3D, 0x00);

ret |= sn65dsi_write_reg(0x3E, 0x00);

ret |= sn65dsi_write_reg(0x0D, 0x00);

msleep(10);

ret |= sn65dsi_write_reg(0x09, 0x00);

msleep(10);

pr_err("[LCD]%s: sn65dsi i2c cmd over \n",__func__);

return ret;

}

//call in HS state

//init seq 9,10,11

void sn65dsi_check_register(void)

{

int ret;

sn65dsi_read_register();

sn65dsi_write_reg(0xE5, 0xFF);

msleep(1);

ret = sn65dsi_read_reg(0XE5);

if(ret != 0){

dev_info(&sn65dsi_data->sn65dsi_chip->dev,"chip sn65dsixx 0xE5 error: 0x%X \n", ret);

}else{

dev_info(&sn65dsi_data->sn65dsi_chip->dev,"chip sn65dsixx 0xE5 success: 0x%X\n", ret);

}

}

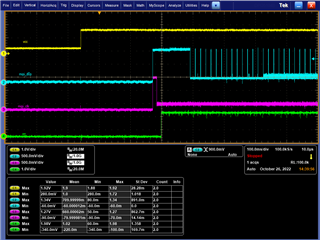

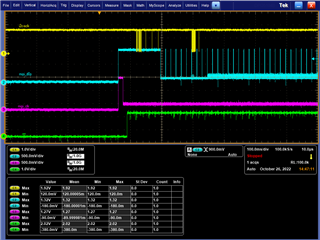

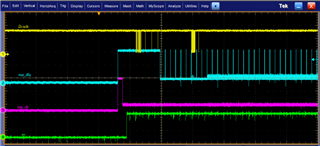

下图是测量时序,图一依次是VCC, MIPI_D0P, MIPI_CLKP, EN.

图二依次是I2C_CLK , MIPI_D0P, MIPI_CLKP, EN

请帮忙看一下,这样的时序哪里有问题?或者i2c初始化PLL, SOFTRESET REG是否正确?

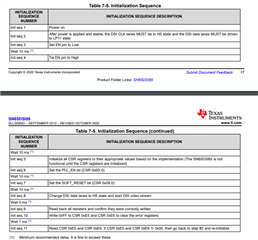

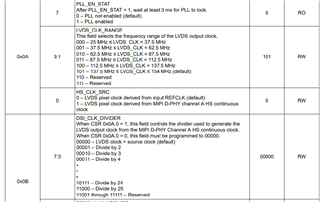

PLL unlock, 有可能是DSI clock的问题,0X0A您配置的为0x05h。 bit0=1说明LVDS的像素时钟来源于HS clock。

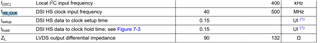

您这边检查下HS_CLK是否满足下面条件:

能够提供联系方式邮箱或者微信,方便进一步确认问题?

抱歉,目前技术在线支持的方式是通过论坛 ,您有什么问题可以随时提出来,我这边也尽快帮您解答。

另外,针对您目前的问题,首先上电后对器件做初始化,建议按照datasheet中的步骤,如果读取E5和E6的寄存器报错,那对其写0XFF进行清零,如果清零后读取还有error,那初始化步骤回到步骤2重新开始,如果这样验证下来还是E5报错,就像我上面提到的检查DSI_CLOCK的信号完整性。

您提到error不断变化,我想和您确认是做了什么动作,发现E5的值不断变化?另外,分别读取的是什么值?

从CLK的波形来看,波形不平滑,duty cycle不稳定,jitter 非常大。也就是说clock信号的完整性很差,所以直接影响到了画面有杂讯。 您是使用的什么作为时钟源?

另外,这篇关于DSI85 single MIPI转dual LVDS配置的FAQ, 步骤非常详细,分享给您,希望对您有所帮助:

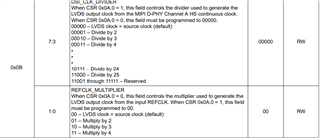

配置27.2M, 3倍频到81.6M。

0x0B您配置的是0x28,即0010 1000.按照您说的倍频3,bit1:0 应该配置为10才对。

1920x1080.pixel clock是1920x1080xfps(30) = 62.208Mhz

另外,这个计算没有算上消隐时间,算上blanking time的话1920x1080xfps(30)需要的像素时钟为74.25Mhz。

0x0B配置的部分,代码部分是先配置为MIPI CLK,但是没显示后,后面有试着配置EVM board上27.2M的外部晶振作为时钟源debug.

所以代码配置和目前的状况有不同步的地方。

现在先总结一下我们目前的状况,

我们现在的开发环境有变化,是我司的MB连接LVDS panel, SN65dsi84 chip在我司的MB上。原理图部分如图一。

图一:

软体配置部分采用的是MIPI CLK,如图二,图三:

配置生成的寄存器列表如图四:

初始化时序如图五:

但是在检查0xE5寄存器的时候,报错0x80,屏幕无显示。

使用Pattern mode生成的寄存器列表,可以显示出彩条。

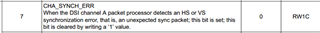

寄存器的解释是,预期外的sync packet,所以请问造成预期外的sync packet原因是什么?

如何系统的排除错误的原因?请帮忙分析原因或者列出您需要的信息。