Other Parts Discussed in Thread: CDCE913

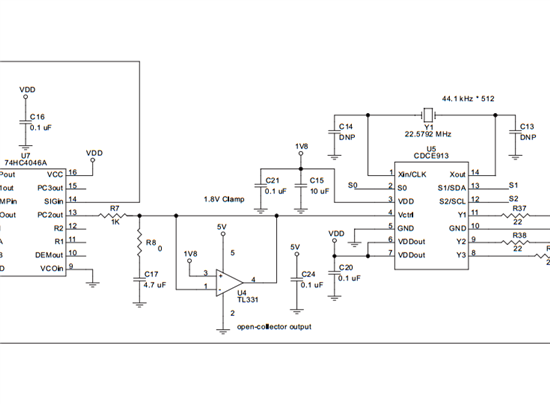

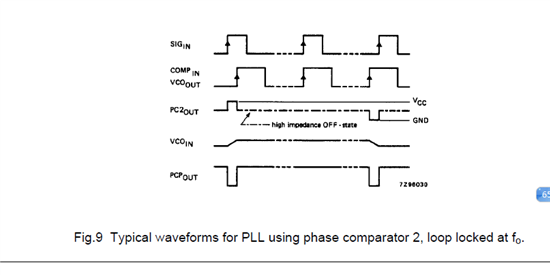

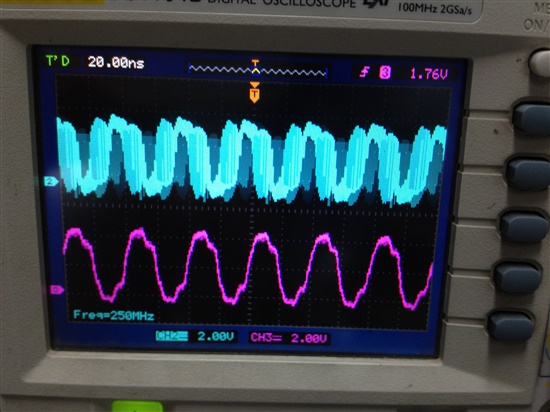

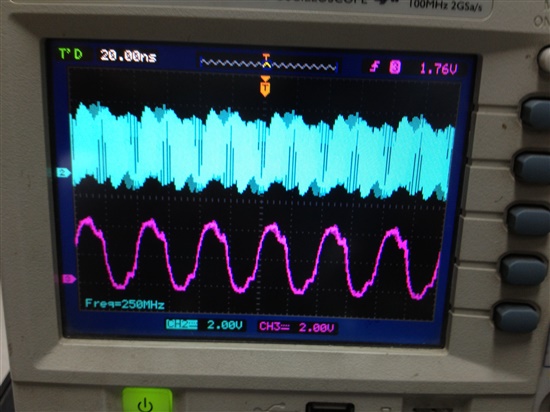

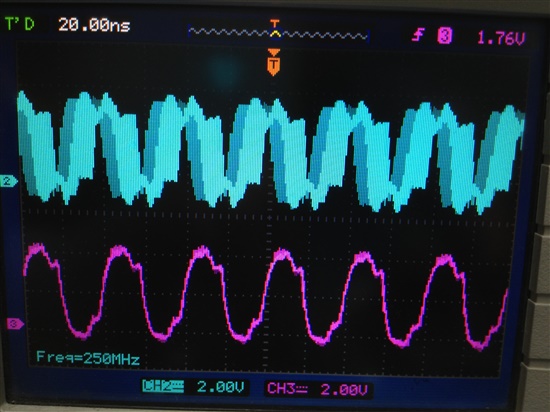

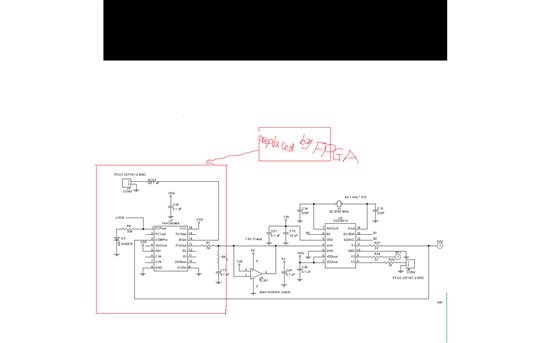

大家好,我用cdce913芯片,XTAl用的是25M的4角晶振。通过FPGA用IIC配置Y1输出的也是25M。然后把Y1输出的25M,和另一个RTL8201芯片输出的25M时钟,同时输入FPGA,通过FPGA将这两个时钟分频成10K的时钟。下图一,是CDCE913的参考电路,我只是用FPGA替换了74HC4046A。两个分频后的时钟相比较用的是图二的方法。但是配置完后用示波器测量发现从CDCE913出来的时钟25M不是很规则,很多毛刺,而且根本没有和RTL8201芯片输出的25M时钟锁相。

不知道问题出在哪里,是不是FPGA的IIC没有将CDCE913配置好,还是什么原因,看了很久的手册,不知道从哪里入手了。望指点。我还需要补充什么没讲到的么?